## U 736 DC CMOS 3 1/2-Digit-Analog-Digital-Wandler

Der U 736 DC ist ein integrierter vollständiger 3 1/2-Digit-Analog-Digital-Wandler mit Hold-Betrieb nach dem Zweiflankenverfahren mit automatischem Nullpunktabgleich in CMOS-Technik.

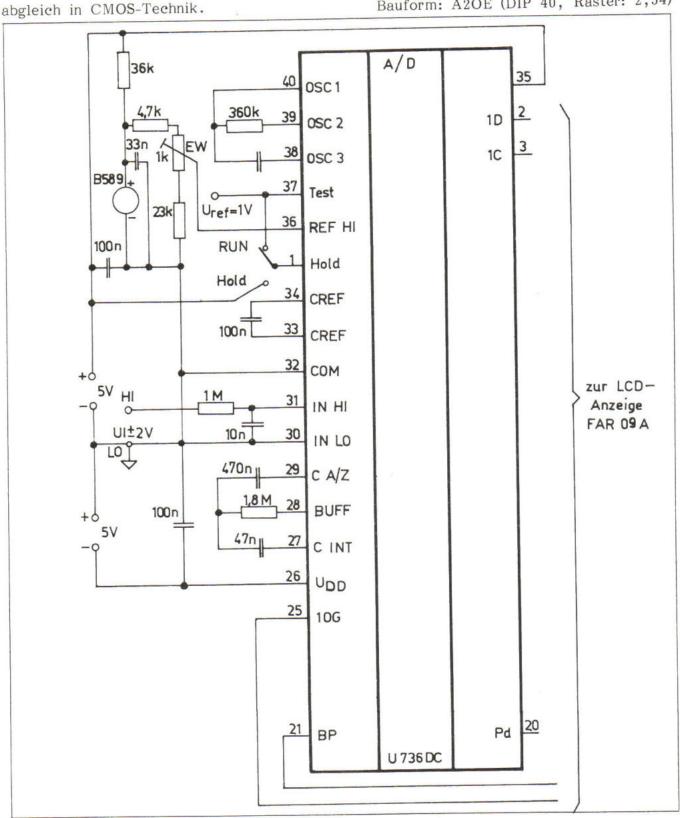

Bauform: A2OE (DIP 40, Raster: 2,54)

Applikationsschaltung Versorgung des U 736 DC mit  $^+$  5 V externe Referenzspannung (U $_{\rm Emax}$ . =  $^+$  2 V)

## Außenbeschaltung:

Der U 736 DC wird mit derselben Außenbeschaltung betrieben wie der C 7136 D, zu beachten ist Anschluß 1 = Hold und Anschluß 35 =  $\rm U_{SS}$ . Der Hold-Anschluß ist ein digitaler Eingang mit einer Schwellspannung, die in der Mitte zwischen  $\rm U_{SS}$  und TEST liegt. Unabhängig vom Pegel am Hold-Anschluß werden Wandlungen durchgeführt. Liegt der Hold-Anschluß an  $\rm U_{SS}$ , wird die Aufdatierung des Anzeigespeichers gesperrt. Bei Anlegen von niedrigem Potential erfolgt eine Aufdatierung am Ende eines jeden Wandlungszyklus. Im Hold-Betrieb wird die niedrigste Verlustleistung erreicht. Der Hold-Anschluß ist CMOS-kompatibel und kann mit einem Schalter zwischen TEST und  $\rm U_{SS}$  betrieben werden. Ein offener Hold-Anschluß wirkt wie Low-Potential (interner pull down). Der Eingang REFLO entfällt. Die Referenzspannung kann zwischen REFHI und COMMON angelegt werden.

## Grenzwerte

| Grenzwert                                          | Kurz-<br>zeichen                     | min.              | max.                       | Einheit |

|----------------------------------------------------|--------------------------------------|-------------------|----------------------------|---------|

| Betriebsspannung                                   | USS                                  | 0                 | +15                        | V       |

| Analogeingangsspannungen                           | U <sub>I30</sub><br>U <sub>I31</sub> | , U <sub>DD</sub> | $^{\mathrm{U}}\mathrm{ss}$ | V       |

| Eingangsspannung bei ex-<br>terner Taktung an OSC1 | U <sub>140</sub>                     | U <sub>TEST</sub> | $^{\mathrm{U}}\mathrm{ss}$ | V       |

Der Eingangsspannungsbereich darf an INHI und INLO bei Begrenzung des Eingangsstromes auf  $\leq 100~\mu A$  überschritten werden.

## Ausgewählte Kennwerte

| Kennwert                | Kurz-<br>zeichen | Meßbedingung | min. | typ. | max. | Einheit |

|-------------------------|------------------|--------------|------|------|------|---------|

| Betriebsspannung        | USS              |              |      | 9    |      | V       |

| Büfferungsausgangsstrom | IOBUFF           |              |      |      | 1    | μΑ      |

| Umgebungstemperatur     | Ta               |              | 0    | +25  | +70  | °C      |

| Taktfrequenz            | fosz             |              |      | 50   | 64   | kHz     |