# Information

U82536 DC, U8036 DC

2/88 (13)

Hersteller: VEB Mikroelektronik "Karl Marx" Erfurt

# Zähler-/Zeitgeber- und paralleler Ein-/Ausgabebaustein

Der Zähler/Zeitgeber- und parallele Ein-/Ausgabebaustein (Counter/Timer and parallel I/O unit) ist ein universeller Peripherieschaltkreis in n-Kanal-Silizium-Gate-Technologie. Er beinhaltet drei I/O-Ports und drei Zähler/Zeitgeber. Seine Funktionen sind programmierbar und können so auf spezielle Anwendungen zugeschnitten werden.

Bild 1: Anschlußbelegung U 82536 DC

Bild 2: Anschlußbelegung U 8036 DC

Der U 82536 DC kann in Systemen mit getrenntem Adreß- und Datenbus wie z. B. U 880-Systemen arbeiten. Der U 8036 DC wird aufgrund seines gemultiplexten Adreß-/Datenbusses vorwiegend in U 8000-Systemen o. a. mit gemultiplextem Bus arbeitenden Prozessorsystemen eingesetzt.

Bild 3: Schaltzeichen U 82536 DC

Bild 4: Schaltzeichen U 8036 DC

## Bezeichnung und Beschreibung der Anschlüsse

PA 0 ... PA 7 Port A (bidirektional, tristate oder open-drain)

Diese acht Leitungen übeftragen Informationen zwischen Port A des CIO und externen Geräten.

PB 0 ... PB 7 Port B (bidirektional, tristate oder open-drain)

Port B wird neben der Funktion analog Port A für den externen Zugriff auf die Zähler/Zeitgeber 1 und 2 benutzt.

PC 0 ... PC 3 Port C (bidirektional, tristate oder open-drain)

Diese vier Ein-/Ausgabeleitungen werden benutzt, um Handshake-, WAIT- und

REQUEST-Leistungen für Port A und B oder den externen Zugriff auf den Zähler/

Zeitgeber drei zu realisieren und den Zugriff auf Port C zu ermöglichen.

PCLK Peripherietakt (Peripheral Clock) - Eingang TTL-kompatibel

Dieser Takt wird für die interne Steuerlogik und für die Zähler/Zeitgeber

benutzt. Er braucht nicht der CPU-Takt zu sein.

INT Interruptanforderung (Interrupt Request) - Ausgang, open-drain, Low-aktiv.

\*Dieses Signal wird aktiviert, wenn der CIO einen Interrupt anfordert.

INTACK Interruptbestätigung (Interrupt Acknowledge) - Eingang, Low-aktiv

Dieses Signal zeigt dem CIO an, daß ein Interruptbestätigungszyklus abläuft.

IEI Interruptfreigabeeingang (Interrupt Enable In) - High-aktiv

Interruptfreigabeausgang (Interrupt Enable Out) - High-aktiv

Diese Signale werden zum Aufbau der Interrupt-Prioritätskette (Daisy-chain)

benutzt, falls mehrere interruptgesteuerte Bausteine im System aktiv sind.

IEI = 1 gibt an, daß kein höherwertiger Baustein einen Interrupt angemeldet hat oder bearbeitet.

## Fortsetzung

IEO ist nur High, wenn IEI High ist und wenn weiterhin gilt:

- 1. Die CPU bearbeitet keinen Interrupt des CIO oder

- Der CIO meldet keinen Interrupt während eines Interruptbestätigungszyklusses an.

#### nur U 8036 DC

AD 0 ... AD 7 Adre8-/Datenbus (Adress Data Bus) - bidirektional, tristate

Der gemultiplexte Bus wird für die Übertragungen zwischen CPU und CIO

benutzt.

AS Adres-Strobe (Eingang, Low-aktiv)

Adressen, INTACK und CS 0 werden abgefragt, während AS = Low ist.

DS Datenstrobe (Eingang, Low-aktiv)

Dieses Signal bestimmt den Zeitpunkt der Datenübertragung. Sind AS und DS

gleichzeitig Low, dann wird der CIO zurückgesetzt.

R/W Lesen/Schreiben (Read/Write) - Eingang

Dieses Signal gibt an, daß die CPU vom CIO liest bzw. in den CIO schreibt.

CS 0, CS 1 Bausteinauswahl (Chip select) - Eingang

CS O und CS 1 müssen gleichzeitig Low bzw. High sein, um den U 8036 DC an-

sprechen zu können. CS 0 wird mit AS übernommen.

# nur U 82536 DC

D 0 ... D 7 Datenbus (bidirektional, tristate)

Der Datenbus wird zur Übertragung zwischen der CPU und dem U 82536 DC be-

nutzt.

RD Lesen (Read) - Eingang, Low-aktiv

Während RD = Low ist, liest die CPU aus dem CIO. Während des Interrupt-

bestätigungszyklusses wird mit RD von der CPU der Interruptvektor gelesen.

WR Schreiben (Write) - Eingang, Low-aktiv

Während WR = Low ist, schreibt die CPU in den CIO. Sind RD und WR gleich-

zeitig Low, wird der CIO zurückgesetzt.

A 0, A 1 AdreBleitungen (Eingänge)

Diese zwei AdreGleitungen dienen zur Auswahl der Portregister oder der Steuer-

register.

CE Bausteinfreigabe (Chip Enable) - Eingang, Low-aktiv

Low-Pegel ermöglicht der CPU, die Register des U 82536 DC zu lesen oder zu

beschreiben.

Bild 5: Gehäuseabmessungen

#### Beschreibung

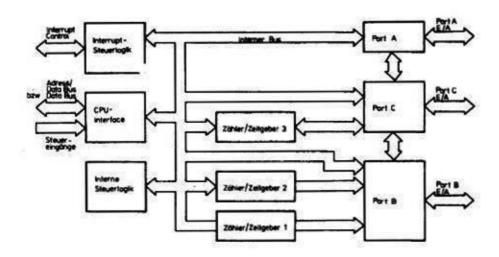

Der CIO besteht aus einem CPU-Interface, drei Ein-/Ausgabeports (zwei universellen 8bit-Ports und einem speziellen 4bit-Port), drei 16bit-Zähler/Zeitgebern und einer Interrupt-Steuerlogik sowie einem internen Steuerlogikblock.

Eine Vielzahl von programmierbaren Funktionen ermöglicht die beste Anpassung an spezielle Anwendungen.

- Es werden zwei Versionen (Bondvarianten) der CIO unterschieden:

- . der U 82536 DC mit CPU-Interface für den U 880 D und für ähnliche Prozessoren (8086, SU-Typ K 1810 WM 86)

- . der U 8036 DC mit Multiplexbus für den U 8000 und für ähnliche Prozessoren

- Alle internen Steuer- und Datenregister sind les- und schreibbar.

- Datenregister sind direkt adressierbar, Steuerregister nur beim U 8036 DC.

- Beim U 82536 DC muß auf die Steuerregister mit einer Befehlsfolge zugegriffen werden.

- Vektorinterrupt inklusive Status (Ursache), Daisy chain (IEI, IEO) und Polling möglich

- WATT/REQUEST-Leitung ermöglicht schnelle DMA-Blockübertragungen in beiden Richtungen (vollduplex).

# Periphere Eigenschaften

- drei unabhängige l6bit-Zähler/Zeitgeber-Kanäle (CT)

- bis zu vier externe Leitungen je CT-Kanal programmierbar: Zählerausgang, Zähler-, Trigger- und Gateeingang (Port B und C)

- drei Signalverläufe am Zähler/Zeitgeberausgang: monostabil (one shot), getaktet (pulsed) und Rechteckimpulse (sequare wave)

- CT 1 und CT 2 sind intern zusammenschaltbar (kaskadierbar).

- Zähler/Zeitgeber retriggerbar oder nicht retriggerbar

- Port A und B sind unabhängige, bidirektionale, doppelt gepufferte 8bit-Ein-/Ausgabeports, programmierbar als Eingang, Impulsfänger, Ausgang, verzögerter Ausgang (Deskew-Timer), Open Drain-Ausgang oder als bidirektionaler Bit-Ports.

- ein 4bit-Spezialport, programmierbar als Port-, Handshake- oder als externe Zähler/Zeitgeber-(CT 3)-Leitungen, Bits einzeln änderbar

- Port A und B doppelt gepuffert

- Interlock-, Strobe-, Impuls- und three-wire-Handshake mit Deskew-Timer

- flexible maskierbare Zeichenerkennungslogik auf Flanken, Zustände oder Änderungen einzelner Bits von Port A und B, programmierbar wie ein 16bit-Vektorinterruptcontroller

- eine Versorgungsspannung von +5 V ± 5 %

- 40poliges DIP-Gehäuse

Bild 6: Blockschaltbild

# $\underline{\text{Grenzwerte}} \quad \text{(Bezugspotential U}_{\text{SS}} = 0 \text{ V)}$

|                       | Kurzzeichen | min. | max. | Einheit | 99 |

|-----------------------|-------------|------|------|---------|----|

| Betriebsspannung      | ucc         | -0,5 | 7    | V       |    |

| Eingangsspannung      | UT          | -0,5 | 7    | v       |    |

| Lagerungstemperaturbe | reich Sto   | -55  | 125  | °c      |    |

Statische und dynamische Kennwerte ( $\sigma_a^b$  = 0 ... 70 °C;  $U_{CC}$  = 5 V ± 0,25 V;  $U_{SS}$  = 0 V)

|                                                    | Kurzzeichen     | min.                 | max.                 | Einheit |

|----------------------------------------------------|-----------------|----------------------|----------------------|---------|

| Eingangsspannung Low                               | UIL             | -0,5                 | 0,8                  | v       |

| Eingangsspannung High                              | UIH             | 2                    | U <sub>CC</sub> +0,3 | V       |

| Takteingangsspannung                               | UICL            | -0,5                 | 0,45                 | ٧ .     |

| 38                                                 | UICH            | U <sub>CC</sub> -0,4 | U <sub>CC</sub> +0,3 | V       |

| Ausgangsspannung Low<br>I <sub>n</sub> = 2 mA      | UOL             |                      | 0,4                  | V       |

| Ausgangsspannung High<br>I <sub>n</sub> = -0,25 mA | U <sub>OH</sub> | 2,4                  | 101                  | V       |

| Stromaufnahme                                      | Icc             |                      | 200                  | mA      |

| Eingangsreststrom                                  | IIL             |                      | 20                   | μA      |

| Ausgangsreststrom                                  | IOL             |                      | 20                   | μA      |

| Taktfrequenz                                       | f               | 0,25                 | 41)                  | MHZ     |

<sup>1) 6</sup> MHz in Vorbereitung

Ausführliche Unterlagen enthält die "Technische Beschreibung CIO U 82536 DC, U 8036 DC" des VEB Mikroelektronik "Karl Marx" Erfurt – Stammbetrieb.

Dieses Datenblatt gibt keine Auskunft über Liefermöglichkeiten und beinhaltet keine Verbindlichkeiten zur Produktion. Die gültige Vertragsunterlage beim Bezug der Bauelemente ist der Typstandard. Rechtsverbindlich ist jeweils die Auftragsbestätigung.

Änderungen im Zuge der technischen Weiterentwicklung vorbehalten.

Die Behandlungsvorschriften für MOS-Bauelemente müssen unbedingt eingehalten werden, da andernfalls eine Reklamation nicht anerkannt werden kann.

Die vorliegenden Datenblätter dienen ausschließlich der Information!

Es konnen daraus keine Liefermöglichkeiten oder Produktionsverbindlichkeiten abgeleitet werden Anderungen im Sinne des technischen Fortschritts sind vorbehalten.

Herausgeber:

veb applikationszentrum elektronik berlin im veb kombinat mikroalektronik

Mainzer Straße 25 Berlin, 1035

Telefon: 5 80 05 21, Telex: 011 2981 011 3055