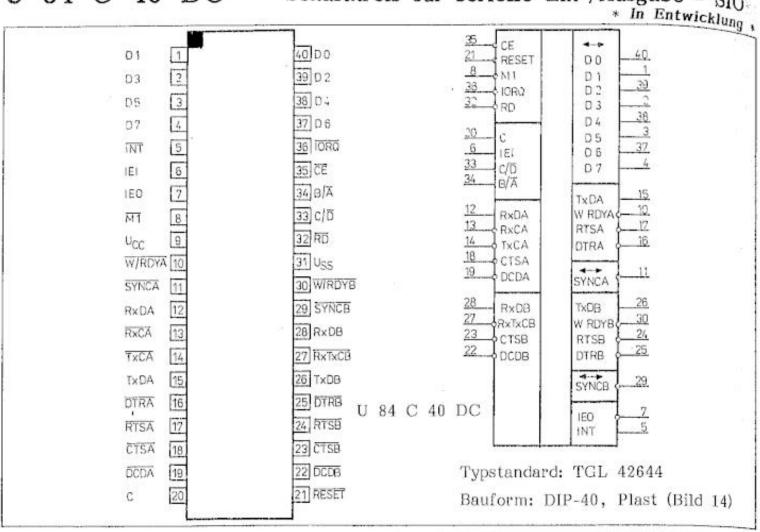

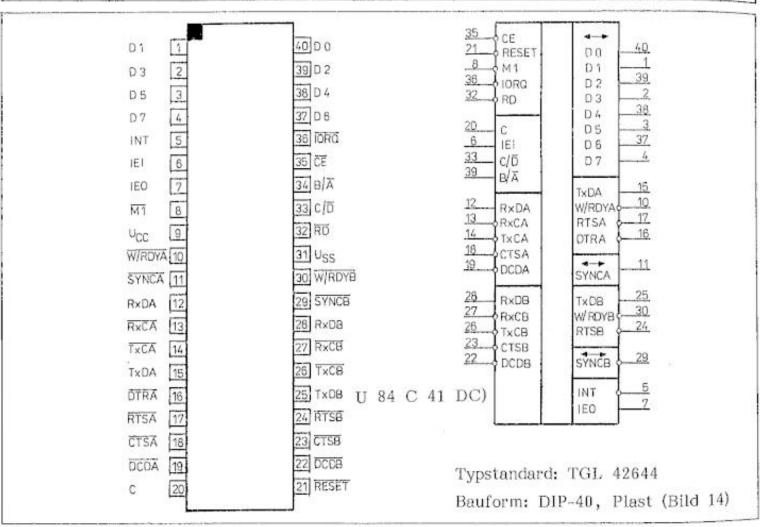

## U 84 C 40 DC

Schaltkreis für serielle Ein-/Ausgabe - SIO

Bezeichnung der Anschlüsse

D0 bis D7

CE

RESET

M1 TORQ

RD

RXDA, RXDB RXCA, RXCB

TXCA, TXCB

CTSA, CTSB

DCDA, DCDB

B/A

C/D

IEI

IEO INT

TXDA, TXDB

W/RDYA, W/RDYB

SYNCA, SYNCB

RTSA, RTSB

DTRA, DTRB

8 Bit bidirektionaler Datenbus

Bausteinauswahl, Eingang

Rücksetzen, Eingang

CPU-Maschinenzyklus M1, Eingang

CPU-Ein-/Ausgabeanforderung, Eingang

CPU-Leseanforderung, Eingang

Empfangsdaten, Eingänge

Empfängertakte, Eingänge<sup>1)</sup>

Sendertakte, Eingänge<sup>1)</sup>

Sendebereitschaft, Eingänge

Datenträgererkennung, Eingänge

Kanalauswahl, Eingang

Umschaltung Steuerwort/Datenwort, Eingang

Interruptfreigabe, Eingang

Interruptfreigabe, Ausgang

Interruptanforderung, Ausgang

Sendedaten, Ausgänge

WAIT/READY-Pin (CPU WAIT, DMA READY), Ausgänge

Externsynchronisation, Ein-/Ausgänge

Sendeanforderung, Ausgänge

Systemtakt

Bereitschaft Datenterminal, Ausgänge

Empfänger- und Sendetakt Kanal B gemeinsam gebondet (U 84 C 40), RxTxCB

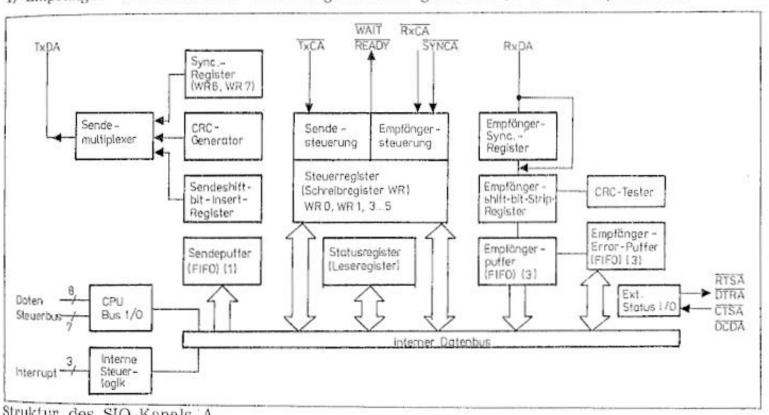

Der SIO ist ein in CMOS-Technologie hergestellter, programmierbarer, zweikanaliger  $B_{\theta \psi}$  stein, der Daten in das für serielle Datenübertragung erforderliche Format umsetzt. Sie kann asynchron, synchron und bitorientiert synchron arbeiten.

## Folgende Varianten werden vom MME gefertigt

| Тур             | Taktfrequenz | Stromaufnahme<br>(typisch) | Schlafzustand |

|-----------------|--------------|----------------------------|---------------|

| U 84 C 40 DC 02 | 2,5 MHz      | 7 mA                       | möglich       |

| U 84 C 40 DC 04 | 4,0 MHz      | 7 mA                       | möglich       |

## Eigenschaften

- Vier unabhängige serielle Ports, zwei Sender- und Empfängerports,

- asynchrone oder synchrone Arbeitsweise,

- asynchrone Daten mit 5, 6, 7 oder 8 Datenbits, 1, 1 1/2 oder 2 Stoppbits und gerader,

ungerader oder keiner Paritätserzeugung bzw. Paritätsprüfung,

- Breakerzeugung und -erkennung, Paritäts-, Überlauf- und Rahmenfehlererkennung,

- alle Ein- und Ausgänge voll TTL-kompatibel,

- Taktvarianten: x 1, x 16, x 32, x 64,

- Datenübertragungsraten: 0 bis 550 kBit/sec,

- 4 Eingänge/4 Ausgänge zur MODEM-Steuerung,

- volle Fähigkeit zur Arbeit nach HDLC einschließlich Verarbeitung des I-Feld-Restes,

- interne oder externe Zeichensynchronisation mit automatischer Einfügung von Synchronisationszeichen und Flags,

- Betriebszustand "Adreßerkennung" bei SDLC/HDLC,

- Betriebszustand "Synchronisationsbyteunterdrückung" mit mono- und bisynchroner Arbeitsweise.

- die hohen Übertragungsraten und die automatische CRC-Erzeugung gestatten die direkte Zusammenschaltung mit Floppy-Disk-Speichern doppelter Dichte, ohne daß direkter Speicherzugriff erforderlich ist,

- empfangene Daten und Fehlerregister sind vierfach, zu sendende zweifach gepuffert,

- leistungsfähige Interruptstruktur durch wahlweise festen oder variablen Interruptvektor,

- CRC-16- oder CRC-CCITT-(0 und -1)-Prüfpolynom,

- gültig empfangene Daten sind vor dem Überschreiben geschützt,

- 5 V Einphasentakt und eine einzige 5 V Gleichspannungsversorgung,

- Prioritätslogik durch Kaskadierung der Bausteine,

- die SIO kann in einen Schlafzustand überführt werden, in dem die Stromaufnahme kleiner als 10 μA wird.