## mikreektronik

# Information

**DL 164 D**

Vergleichstyp: SN 74 LS 164 N

8-bit-Schieberegister

Vorläufige technische Daten

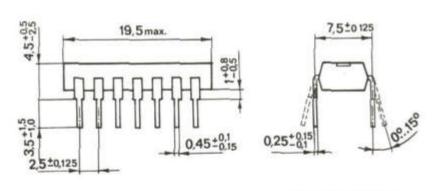

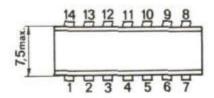

Gehäuse: 14poliges DIL-Plastgehäuse

Bauform: 21.2.1.2.14 nach TGL 26 713

Masse: ≤ 1,5 g

Rastermaß: 2,5  $\pm$  0,125 mm

Reihenabstand: 7,5 mm

21. 2. 1. 2.14 TGL 26713

#### Pinbelegung:

| Pin Symbol |       | Beschreibung      | Pin | Symbol         | Beschreibung        |  |  |

|------------|-------|-------------------|-----|----------------|---------------------|--|--|

| 1 A)       | A )   |                   | 8   | CLK            | Takteingang         |  |  |

| 2          | B )   | serielle Eingänge | 9   | CLR            | Rücksetzeingang CLR |  |  |

| 3          | $Q_A$ | Ausgang           | 10  | $Q_{E}$        | Ausgang             |  |  |

| 4          | QB    | Ausgang           | 11  | $Q_F$          | Ausgang             |  |  |

| 5          | Qc    | Ausgang           | 12  | $Q_G$          | Ausgang             |  |  |

| 6          | Qp    | Ausgang           | 13  | Q <sub>H</sub> | Ausgang             |  |  |

| 7          | M     | Masse             | 14  | Ucc            | Betriebsspannung    |  |  |

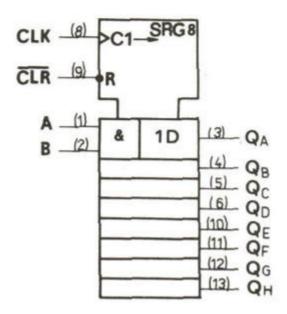

#### Logikschaltbild:

L164 A1 E 85

Der Schaltkreis DL 164 D ist ein 8-bit seriell-EIN/parallel-AUS Schieberegister. Die seriellen Daten werden durch ein UND-Gatter mit 2 Eingängen (A u. B) synchron mit der Low/High-Flanke des Taktes übernommen. Mit dem Rücksetzeingang CLR können unabhängig vom Takt alle Registerausgänge nach Low geschaltet werden. Das Schieberegister eignet sich für Serien-Parallel-Umsetzung bis zu einer maximalen Taktfrequenz von 25 MHz.

#### Funktionstabelle:

| Eingänge |     |   | Ausgänge |                 |                |                |

|----------|-----|---|----------|-----------------|----------------|----------------|

| CLR      | CLK | Α | В        | $Q_A$           | Q <sub>B</sub> | Q <sub>H</sub> |

| L        | X   | × | Х        | L               | L              | L              |

| Н        | L   | X | ×        | Q <sub>AO</sub> | $Q_{BO}$       | QHO            |

| Н        | 1   | Н | Н        | Н               | $Q_{An}$       | $Q_{Gn}$       |

| H        | 1   | L | ×        | L               | $Q_{An}$       | $Q_{Gn}$       |

| Н        | 1   | X | L        | L               | $Q_{An}$       | $Q_{Gn}$       |

H ≙ High-Pegel

L ≙ Low-Pegel

X \_ beliebieger Pegel (Low oder High)

↑

Low-High-Flanke

$Q_{AO}$ ,  $Q_{BO}$ ,  $Q_{HO}$  = Pegel von  $Q_{A}$ ,  $Q_{B}$  bzw.  $Q_{H}$ , bevor die statischen Eingangsbedingungen angelegt werden.

$Q_{An}$ ,  $Q_{Gn}$  = Pegel von  $Q_A$  bis  $Q_G$  vor der letzten Schaltflanke an CLK.

#### Grenzwerte:

|                  |     | min. | max. |   |

|------------------|-----|------|------|---|

| Betriebsspannung | Ucc | 0    | 7    | V |

| Eingangsspannung | Uı  | -    | 7    | V |

### Betriebsbedingungen (gültig für den Betriebstemperaturbereich):

|                       |                 | min. | max. |    |

|-----------------------|-----------------|------|------|----|

| Betriebsspannung      | Ucc             | 4,75 | 5,25 | V  |

| L-Eingangsspannung    | UIL             | -    | 0,8  | V  |

| H-Eingangsspannung    | UIH             | 2    | -    | V  |

| L-Ausgangsstrom       | IOL             | -    | 8    | mA |

| H-Ausgangsstrom       | $-I_{OH}$       | -    | 0,4  | mA |

| Impulsdauer CLR, CLK  | t <sub>w</sub>  | 20   | -    | ns |

| Haltezeit CLK A, B    | th              | 5    | -    | ns |

| Voreinstellzeit A, B, | t <sub>su</sub> |      |      |    |

| CLK                   |                 | 15   | -    | ns |

| Umgebungstemperatur   | 9 <sub>a</sub>  | 0    | 70   | °C |

| max. Taktfrequenz     | $f_{max}$       | -    | 25   | ns |

Statische Kennwerte (bei  $U_{CC} = 5.0 \text{ V} \pm 0.25 \text{ V}$ ;  $\vartheta_a = 0 \text{ bis } 70 \text{ °C}$ ):

|                                                   |                 | min. | max. |    |

|---------------------------------------------------|-----------------|------|------|----|

| Stromaufnahme                                     | Icc             |      |      |    |

| $U_{CC} = 5,25 \text{ V}^1$ )                     |                 | -    | 27   | mA |

| Ausgangskurzschlußstrom                           | -Ios            |      |      |    |

| $U_{CC} = 5,25 V^2$                               |                 | 20   | 100  | mA |

| H-Ausgangsspannung                                | UoL             |      |      |    |

| $U_{CC} = 4,75 \text{ V}$                         |                 |      |      |    |

| $I_{OL} = 4$ mA                                   |                 | -    | 0,4  | V  |

| $I_{OL} = 8$ mA                                   |                 | -    | 0,5  | V  |

| H-Eingangsstrom                                   | I <sub>IH</sub> |      |      |    |

| $U_{CC} = 5,25 \mathrm{V}$                        |                 |      |      |    |

| $U_{1H} = 2.7 \text{ V}$                          |                 | 770  | 20   | μА |

| $U_{IH} = 7$ V                                    |                 | -    | 100  | μА |

| L-Eingangsstrom                                   | $-I_{1L}$       |      |      |    |

| $U_{CC} = 5,25 \text{ V}, U_{IL} = 0,4 \text{ V}$ |                 | -    | 360  | μА |

| Clampingspannung der Eingangsdiode                | $-U_1$          |      |      |    |

| $U_{CC} = 4,75 \text{ V}; -I_1 = 18 \text{ mA}$   |                 | -    | 1,5  | V  |

<sup>1)</sup> Eingänge A und B auf 0 V, CLK auf 4,5 V, CLR kurzzeitig auf 0 V und anschließend auf 4,5 V legen; Ausgänge offen.

Dynamische Kennwerte: ( $U_{CC} = 5.0 \text{ V} \pm 55 \text{ mV}$ ;  $\vartheta_a = 0 \text{ bis 70 °C}$ )

|                |        |            |                  | min. | max. |    |

|----------------|--------|------------|------------------|------|------|----|

| Signalver      | zögeri | ungszeiten |                  |      |      |    |

| $U_{CC} = 5 V$ |        |            | t <sub>pHL</sub> | _    | 36   | ns |

|                | CLK    | Q          | tpLH             | -    | 27   | ns |

|                |        |            | t <sub>pHL</sub> | -    | 32   | ns |

Bestellbezeichnung: Integrierter Schaltkreis DL 164 D.

Änderungen, dem technischen Fortschritt entsprechend, behalten wir uns vor. Sollten beim Einsatz der Bauelemente Fragen auftreten, wenden Sie sich an uns. Ein erfahrenes Ingenieurkollektiv hilft Ihnen, Problemlösungen zu finden.

Ag 05/021/86

veb halbleiterwerk frankfurt/oder im veb kombinet mikroelektronik DDR 1200 Frankfurt/Oder - Telefon 4 60

Volkseigener Außenhandelsbetrieb der Deutschen Demokratischen Republik DDR - 1026 Berlin, Alexande platz 6 Haus der Elektroindustrie

<sup>&</sup>lt;sup>2</sup>) zulässige Prüfzeit ≤ 1 s, Kurzschluß nur an einem Ausgang zulässig.