# 4 Dekaden Vor-/Rückwärtszähler U 125 D

Der integrierte MOS-Schaltkreis U 125 D ist ein in n-Kanal-Silicon-Gate-Technik ausgeführter 4-Dekaden-Vor-/Rückwärtszähler mit Zusatzfunktionen. Der U 125 D kann in der Meß- und Regeltechnik einsetzt werden. Er ist für den Einsatz in Zählgeräten vorgesehen.

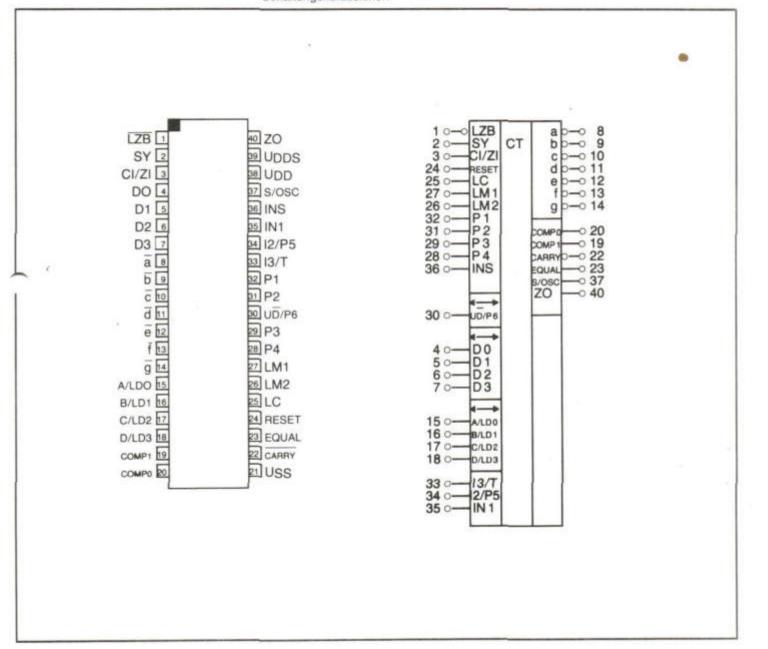

Bild 1: Anschlußbelegung und Schaltungskurzzeichen

### Bezeichnung der Anschlüsse

| LZB      | Vornulienunterdrückung | ZO    | Nullausgang                         |

|----------|------------------------|-------|-------------------------------------|

| SY       | Synchronisierung       | UDDS  | gepufferte Betriebsspannung         |

| CI/ZI    | Takt-/Nulleingang      | Upp   | Betriebsspannung                    |

| D0       | Dezimalstelle 0        | S/OSC | Vorzeichenausgang, Ausgang Teiler   |

| D1       | Dezimalstelle 1        | INS   | Vorzeicheneingabe                   |

| D2       | Dezimalstelle 2        | IN 1  | Zähleingang 1                       |

| D3       | Dezimalstelle 3        | 12/P5 | Zähleingang 2, Programmiereingang 5 |

|          |                        | 13/T  | Zähleingang 3, Teilertest           |

| a b c d  |                        | P 1   | Programmiereingang 1                |

| c        |                        | P 2   | Programmiereingang 2                |

| d        | 7-Segment-Ausgänge     | UD/P6 | Vor-/Rückwärtsumschaltung,          |

| <u>ē</u> |                        |       | Programmiereingang 6                |

| f        |                        | P 3   | Programmiereingang 3                |

| g        |                        | P 4   | Programmiereingang 4                |

|          |                        | LM 1  | Laden Speicher 1                    |

| A/LD 0   |                        | LM 2  | Laden Speicher 2                    |

| B/LD 1   | BCD-Ein-/Ausgänge      | LC    | Laden Zähler                        |

| C/LD 2   | (Load Digit            | RESET | Rücksetzeingang                     |

| D/LD3    |                        | EQUAL | Koinzidenausgang                    |

| COMP 1   |                        | CARRY | Übertragausgang                     |

| COMP 0   | Komparatorausgänge     | Uss   | Bezugspotential                     |

### Beschreibung

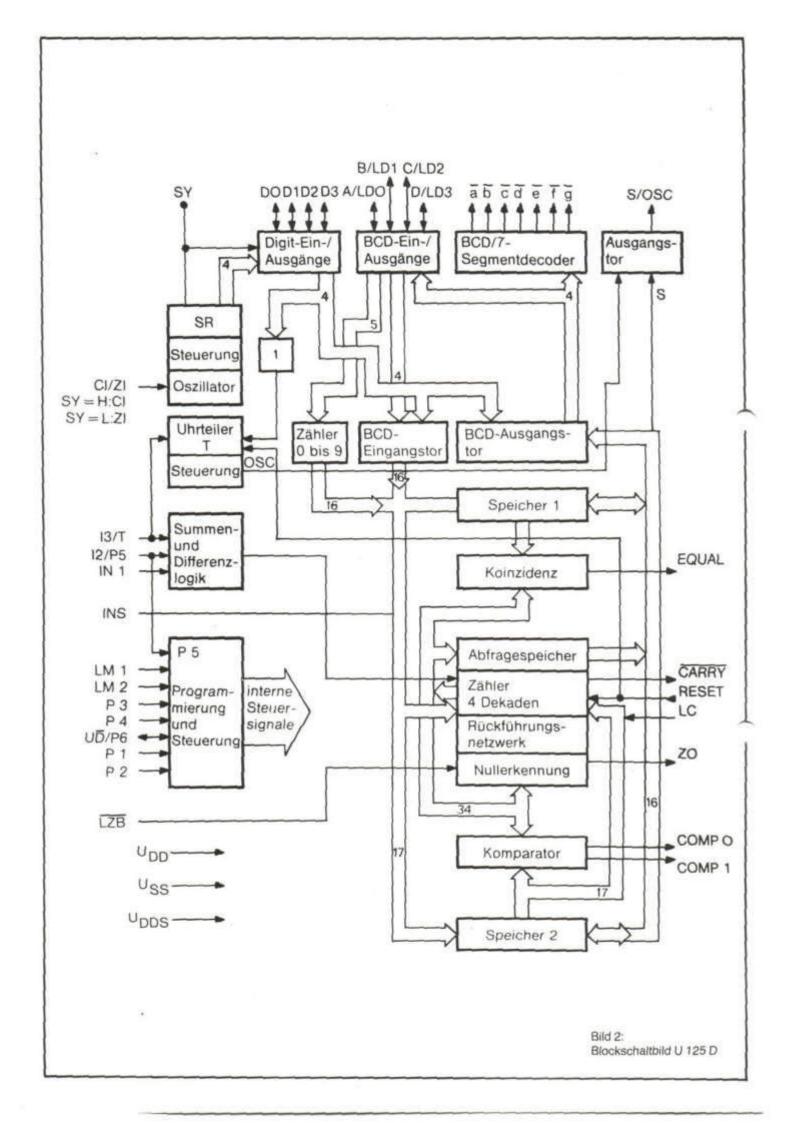

Der Schaltkreis U 125 D ist ein programmierbarer vierstelliger dekadischer Vor-/ Rückwärtszähler (siehe Bild 2). Er enthält 2 Speicher, deren Inhalt mit dem Zählerstand verglichen wird.

Über entsprechende externe Treiber ist es möglich, 7-Segmentanzeigebauelemente (LED) im Multiplexbetrieb anzusteuern. Gleichzeitig steht die Ausgangsinformation auch im BCD-Format an den entsprechenden Ein-/Ausgängen zur Verfügung.

An den 3 Zähleingängen ist eine Summenund Differenzlogik angeschlossen, die es gestattet, in bestimmten Betriebsarten mehrere, auch gleichzeitig auftretende Impulse zu zählen.

In den Betriebsarten Summen- und Differenzzähler ist der Zählerstand im Pufferbetrieb nicht gesichert.

Für den Betrieb als Uhr enthält der Schaltkreis einen 215-Vorteiler und die Logik zur Erzeugung von 100 Hz- und 1/60 Hz-Impulsen. Bei Ausfall der Betriebsspannung UDD ist es möglich, den Inhalt der Speicher und den aktuellen Zählerstand zu erhalten, wenn dafür gesorgt ist, daß am Anschluß Upos die Spannung nicht unter 2 V absinkt. Die Eingänge RESET, LC, P 3, P 4, LM 1, LM 2, UD/P 6, IN 1, I 3/T, 12/P 5 und INS sind mit internen Triggerschaltungen versehen. Die Eingänge P 1, P 2 und SY werden mit Hilfe integrierter Pull up-Widerstände in unbeschaltetem Zustand auf UDDS-Potential gezogen. Die Kaskadierung mehrerer Schaltkreise ist möglich.

Um Funktionsstörungen der Zählkaskaden im Pufferbetrieb zu vermeiden, muß in diesem Falle die Verbindung Übertrag-Zähleingang über einen Lastwiderstand (Richtwert 10 kOhm) mit der Batteriespannung verbunden werden. Mittels der beiden Programmiereingänge P 1 und P 2 sowie der Eingänge UD/P 6 und I 2/P 5 lassen sich alle Betriebsarten einstellen. Folgende Grundbetriebsarten sind möglich:

| P1 | P 2 | Betriebsart | Bezeichnung          |

|----|-----|-------------|----------------------|

| н  | н   | 1           | direkter Zählbetrieb |

| H  | L   | 2           | Summenzähler         |

| L  | Н   | 3           | Differenzzähler      |

| L  | E.  | 4           | Uhrenbetrieb         |

Für die ersten drei Betriebsarten gilt, daß bei Nulldurchgang des Zählers automatisch Zählrichtung und Vorzeichen umgeschaltet werden.

| Betriebsart: | direkter Zählbetrieb                                            |

|--------------|-----------------------------------------------------------------|

| IN 1:        | Eingang des Zählers mit einer maximalen Zählfrequenz von 2 MHz, |

|              | gezählt wird jeweils die H/L-Flanke                             |

S/OSC: Ausgang Vorzeichen (H = -, L = +)

12/P 5: mit P 5 lassen sich zwei Zählweisen einstellen:

P 5 = L - dekadischer Zähler bis "9999"

P 5 = H - die beiden höherwertigen Digits zählen dekadisch, die

niederwertigen sexagesimal bis "9923"

UD/P 6: mit UDwird die Zählrichtung umgeschaltet:

UD = H - vorwärts UD = L - rückwärts

Betriebsart 2: dekadischer Summenzähler IN 1, I 2 / P 5 sind verknüpfte Zähleingänge

IN 1, 12/P 5 sind verknüpfte Zähleingänge, d. h. jeder der an einem der drei Einund I 3/T: gänge auftretende Zählimpuls (H/L-Flanke) wird erkannt und je nach Programmierung von UD azugezählt oder abgezogen. Die

maximale Zählfrequenz beträgt bei dieser Programmierung für jeden Eingang 50 kHz.

UD/P 6: steuert die Zählrichtung (H = vorwärts, L = rückwärts) s/OSC: ist Ausgang des Vorzeichens (H = -, L = +)

Betriebsart 3:

dekadischer Differenzzähler

IN 1, 12/P 5:

sind verknüpfte Zähleingänge, dabei bewirkt jeder an IN 1 ankommende Zählimpuls (H/L-Flanke) ein Vorwärtszählen und jeder an 12 ankommende Impuls ein Rückwärtszählen des Zählers. Die maximale

Zählfreguenz beträgt dabei 50 kHz.

UD/P 6:

ist hier Ausgang, der die momentane Zählrichtung des internen Zäh-

lers anzeigt (H = vorwärts, L = rückwärts).

S/OSC:

gibt das Vorzeichen an (H = -, L = +)

Betriebsart 4:

Uhrenbetrieb

Bei dieser Programmierung ist intern die Zählrichtung "vorwärts" festgelegt, wobei UD/P 6 und I 2/P 5 als Programmiereingänge für die verschiedenen sexagesimalen Zählweisen benutzt werden.

Der Ausgang S/OSC ist hierbei Ausgang des integrierten Vorteilers. Wird an den Eingang CI/ZI eine Frequenz von 32768 Hz angelegt, so erhält man am Ausgang OSC die unten angegebenen Frequenzen, die dann direkt auf den Zähleingang IN 1 gelegt werden können.

| P5 | P6 | Zählumfang | osc  | (be     | 32,768 kHz)                                 |

|----|----|------------|------|---------|---------------------------------------------|

| L  | L  | 2359       | 1/60 | 1707120 |                                             |

| L  | н  | 5999       | 100  | Hz      | (nur wenn OSC an IN 1<br>angeschlossen ist) |

| H  | L  | 5959       | 1    | Hz      |                                             |

| H  | н  | 2359       | 1/60 | Hz      |                                             |

### Anzeige- und Steuervarianten

Die Steuerung der Datenein- bzw. -ausgabe, der Anzeige, der Zählwertspeicherung, der Zählwertübernahme in die Speicher und die der "Blanking"-Funktion erfolgt über die Steuereingänge P 3, P 4 LM 1 und LM 2. Bei Übergängen zu anderen Anzeige- und Steuervarianten müssen unerwünschte Programmierzustände vermieden werden.

Damit ergeben sich die folgenden 16 Varianten:

#### 1. LM 1, LM 2, P3, P4:

Anzeige Abfragespeicher einschließlich Vorzeichen; BCD-Ausgänge (Der Abfragespeicher übernimmt ständig den aktuellen Thlerstand und das Vorzeichen des Zäh-

2. LM 1, LM 2, P 3, P 4;

Anzeige Speicher 1 einschließlich Vorzeichen; BCD-Ausgänge

3. LM 1, LM 2, P 3, P 4:

Anzeige Speicher 2 einschließlich Vorzeichen; BCD-Ausgänge

4. LM 1. LM 2. P 3. P 4:

Anzeige Abfragespeicher einschließlich Vorzeichen: BCD-Ausgänge (Die Übernahme des aktuellen Zählerstandes imolusive Vorzeichen ist unterbrochen "Abfragefunktion").

5. LM 1, LM 2, P 3, P 4:

Das Ausgangssignal der Summen-/Differenzlogik wird über den Ausgang CARRI ausgegeben.

6. LM 1, LM 2, P3, P4; analog Punkt 4.

7. LM 1, LM 2, P 3, P 4:

"blanking"; keine Anzeige:

Ausgänge a bis g

Ausgang S/OSC an pull-up-Elementen (Depletion-Transistor)

BCD-Ein-/Ausgänge

8. LM1, LM 2, P3, P4:

Digitsynchrone Dateneingabe über BCD-Eingänge und Vorzeicheneingabe über Eingang INS (H = -, L = +) in den Zähler. Die Anzeige erfolgt über den Abfragespeicher, der ständig den aktuellen Zählerstand übernimmt (inclusive Vorzeichen). Zählvorgang ist unterbrochen.

9. LM 1, LM2, P3, P4:

Digitsynchrone Dateneingabe über BCD-Eingänge und Vorzeicheneingabe über Eingang INS in den Speicher 1. Anzeige Speicher 1 einschließlich Vorzeichen Speicher 1.

10. LM 1, LM 2, P 3, P 4:

Digitsynchrone Dateneingabe über BCD-Eingänge, und Vorzeicheneingabe über Eingang INS in den Speicher 2 einschließlich Vorzeichen Speicher 2.

11. LM 1, LM 2, P 3, P 4;

Dekadenweise zählende Dateneingabe mittels intern getaktetem Ringzähler (0 bis 9) in den Zähler. Dekadenwahl mittels statischer BCD-Eingänge und Vorzeicheneingabe über Eingang INS (Vorzeichenwechsel bei jeder L/H-Flanke) in den Zähler. Anzeige Abfragespeicher (einschließlich Vorzeichen), der ständig Vorzeichen und aktuellen Zählerstand übernimmt. Zählvorgang ist unterbrochen, wenn an INS oder BCD-Eingängen der logische Pegel ..H" anliegt. Bemerkung: siehe Seite 11:

12. LM 1, LM 2, P 3, P 4:

Dekadenweise zählende Dateneingabe mittels intern getaktetem Ringzähler (0 bis 9) in den Speicher 1. Dekadenwahl mittels statischer BCD-Eingänge und Vorzeicheneingabe über Eingang INS (Vorzeichenwechsel bei jeder L/H-Flanke) in den Speicher 1. Anzeige Speicher 1 und Vorzeichen Speicher 1.

13. LM 1, LM 2, P 3, P 4:

analog zu Punkt 12. Betrifft Speicher 2

14. LM 1, LM 2, P3, P4:

Anzeige Abfragespeicher mit Vorzeichen. BCD-Ausgänge: die Übernahme des Zählerstandes in den Abfragespeicher ist unterbrochen; Speicher 1 übernimmt Vorzeichen und Zählerstand des Abfragespeichers.

15. LM 1, LM 2, P3, P4:

analog zu Punkt 14. Betrifft Speicher 2

16. LM 1, LM 2, P3, P4:

keine Anzeige, d. h. Ausgänge a bis g sind an pull-up-Elementen (Depletion-Transistor), BCD-Ausgänge und Ausgabe Vorzeichen Abfragespeicher; (Abfragespeicher übernimmt ständig Vorzeichen und aktuellen Stand des Zählers).

## veb mikroelektronik karl marx erfurt

DDR-5023 Erfurt, Rudolfstraße 47 Telefon 5.80, Telex 061 306

## elektronik export.import

Volkseigener Außenhandelsbetrieb der Deutschen Demokratischen Republik DDR - 1026 Berlin, Alexanderplatz 6 Telex: BLN 114721 elei, Telefon: 2180

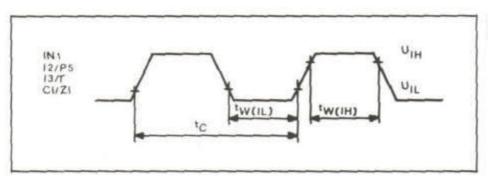

Bild 3: maximale Taktfrequenz

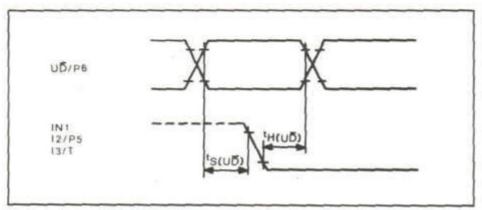

Bild 4: Zählrichtungsumschaltung mit UD/P 6

Dieses Informationsblatt gibt keine Auskunft über Liefermöglichkeiten und beinhaltet keine Verbindlichkeiten zur Produktion. Die gültige Vertragsunterlage beim Bezug der Bauelemente ist der Typstandard. Rechtsverbindlich ist jeweils die Auftragsbestätigung.

Änderungen im Zuge der technischen Weiterentwicklung vorbehalten. Die Behandlungsvorschriften für MOS-Bauelemente sind unbedingt einzuhalten, da andernfalls eine Reklamation nicht anerkannt werden kann.

### Grenzwerte

|       |      | and the same of the same of |       |

|-------|------|-----------------------------|-------|

| V (I) | -10. | 79.05                       | 1     |

| 117 = | -111 | 711                         | 10.00 |

| 100   |      |                             | . ~   |

| Kennwert                                                                              | Kurz-<br>zeichen                                                      | min.                | max.                 | Einhei           |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------|----------------------|------------------|

| Betriebsspannung<br>Eingangsspannung<br>Lagerungstemperaturbereich<br>Verlustleistung | $V_{DD}$ $U_{i}$ $\theta_{sing}$ $P(\vartheta_{sing} = 25^{\circ} C)$ | -0,5<br>-0,5<br>-55 | 7<br>7<br>125<br>0,7 | V<br>V<br>©<br>W |

### Statische Kennwerte

| Kennwert                                                                                     | Kurz-<br>zeichen                   | min.    | max.      | Einheit          |

|----------------------------------------------------------------------------------------------|------------------------------------|---------|-----------|------------------|

| Betriebsspannung                                                                             | Upp                                | 4,75    | 5,25      | V                |

| gepufferte Betriebsspannung ()                                                               | Upps                               | 2       | 5,25      | V                |

| gepufferte Betriebsspannung 2)                                                               | Upps                               | 4,75    | 5,25      | V<br>V<br>V<br>V |

| Eingangsspannung L                                                                           | UIL                                | -0,5    | 0,8       | V                |

| Eingangsspannung H                                                                           | U <sub>IH</sub>                    | 2,4     | Upp       | 1 v              |

| Takteingangsspannung L 3)                                                                    | VILC                               | -0,5    | 0,45      | V                |

| Takteingangsspannung H 3)                                                                    | Unito                              | Upp-2,0 | Upp       | V                |

| Ausgangsspannung L. bei I <sub>0</sub> = 1,8 mA                                              | UoL                                |         | 0.4       | V                |

| Ausgangsspannung H bei I <sub>0</sub> = 0,25 mA<br>für D 0 D 3, EQUAL, COMP 0, COMP 1, S/OSC | U <sub>OH</sub>                    | 2,75    | CONTROLL. | V                |

| Ausgangsspannung H bei $I_0 = -0.25 \text{ mA}$ für sonstige Ausgänge                        | , U <sub>OH</sub>                  | 2,4     |           | V                |

| Stromaufnahme                                                                                | Ipp                                | 1 1     | 80        | mA               |

| Stromaufnahme stand-by  1) U <sub>DD</sub> = 0 V 2) U <sub>DD</sub> = 5 V 3) nur Eingang CI  | I <sub>DD</sub><br>I <sub>SB</sub> | }       | 80<br>5   | mA               |

### Dynamische Kennwerte

| Kennwert                                          | Kurz-<br>zeichen   | min.       | max. | Einheit |

|---------------------------------------------------|--------------------|------------|------|---------|

| a) direkte Zählweise                              |                    |            |      |         |

| Taktperiode an IN 1                               | to                 | 500        | )    | ns      |

| High-Breite des Taktes an IN 1                    | twon.              | 240        | 1    | ns      |

| Low-Breite des Taktes an IN 1                     | t <sub>W(IL)</sub> | 240        | 1    | ns      |

| Setzzeit für Zählrichtungsumschaltung mit UD/P 6  | t <sub>s(ub)</sub> | 1          |      | μs      |

| b) Summe-Differenz-Zählweise                      | 1 1                |            |      | 1       |

| Taktperiode an IN 1, I 2/P 5, I 3/T               | tosd               | 20         |      | Jus     |

| High-Breite des Taktes an IN 1, I 2/P 5, I 3/T    | t <sub>w(iH)</sub> | 500        | Į.   | ns      |

| Low-Breite des Taktes an IN 1, 12/P 5, 13/T       | t <sub>W(IL)</sub> | 19         |      | μs      |

| c) Summe-Zählweise                                | 1                  |            |      | }       |

| Setzzeit für Zählrichtungsumschaltung mit UD/P 6  | ts(up)             | 100        | 1    | μs      |

| Haltezeit für Zählrichtungsumschaltung mit UD/P 6 | t <sub>H(UD)</sub> | 40         |      | μs      |

| d) CI/ZI als Takteingang                          |                    |            |      | 1       |

| Taktperiode an CI/ZI                              | tc                 | 2,5        |      | us      |

| High-Breite des Taktes an CI/ZI                   | twichi             | 1,2<br>1,2 | Į.   | Jus     |

| Low-Breite des Taktes an CI/ZI                    | t <sub>W(CL)</sub> | 1,2        |      | μs      |

|                                                   | 1                  |            |      | 1       |

|                                                   | 1 - 1              |            |      | 1       |

|                                                   | 1 1                |            |      | 1       |

| (4.5                                              | 1 1                |            |      | 1       |

|                                                   |                    |            |      | }       |

|                                                   | }                  |            |      | 1       |

|                                                   | 1 1                |            | 1    | 1       |