## mikreektronik

# Information

## 64 k x 1 dynamischer RAM U 2164 D

Vorläufiges Datenblatt!

Der integrierte Schaltkreis U 2164 D ist ein dynamischer RAM in n-Kanal-Silicon-Gate-Technologie mit wahlfreiem Zugriff und einer Speicherkapazität von 65 536 bit in einer Organisation von  $64 \text{ k} \times 1$ .

Durch das Multiplexen der Adreßsignale ist der Einsatz des platzsparenden lépoligen Dual-in-line-Gehäuses möglich. Der Schaltkreis ist für den Aufbau von RAM-Blöcken verschiedener EDVA-Systeme, Mikrorechner und Automatisierungseinrichtungen bestimmt.

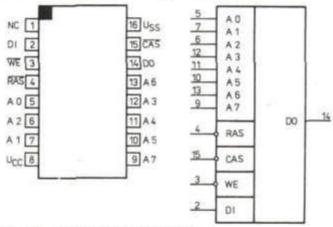

Bild 1: Anschlußbelegung und Schaltungskurzzeichen Bezeichnung der Anschlüsse:

| DUZ  | erennand | ner wildrutness:                         |      |                 |                     |

|------|----------|------------------------------------------|------|-----------------|---------------------|

| 1    | NC       | nicht angeschlossen                      | 9    | A 7             | Adresseneingang     |

| 2    | DI       | Dateneingang                             | 10   | A 5             | Adresseneingang     |

| 3    | WE       | Schreibsignal                            | 11   | A 4             | Adresseneingang     |

| 4    | RAS      | Eingang des Signals<br>der Zeilenauswahl | 12   | A 3             | Adresseneingang     |

| 5    | A D      |                                          | 13   | A 6             | Adresseneingang     |

| - 33 | 200      | Adresseneingang                          | 14   | DO              | Datenausgang        |

| 6    | A 2      | Adresseneingang                          | 15   | CAS             | Eingang des Signals |

| 7    | A 1      | Adresseneingang                          | 1.53 | STATE OF        | zur Spaltenauswahl  |

| 8    | ucc      | Betriebsspannung +5 V                    | 16   | U <sub>SS</sub> | Bezugspotential     |

|      |          |                                          |      |                 |                     |

Bild 2: Gehäuseabmessungen

#### Kurzbeschreibung

- dynamischer RAM in der Organisation von 65 536 x 1 bit

- RAS-Zugriffszeit/Zykluszeit:

200 ns/330 ns (U 2164 D 20)

250 ns/460 ns (U 2164 D 25)

- Betriebsspannung:

- geringe Stromaufnahme:

+5 V + 10 %

55 mA (Betriebsstrom)

5 mA (Ruhestrom)

- getrennter Datenein- und -ausgang

- tristate-Ausgangsstufen, Datenausgang durch CAS-Signal steuerbar

- Eingangsspannung darf kurzzeitig  $U_{

m IL}$  = -2 V betragen

- Ein- und Ausgänge TTL-kompatibel

- Betriebsarten: READ

WRITE

READ-MODIFY-WRITE

PAGE-MODE

RAS-ONLY-REFRESH

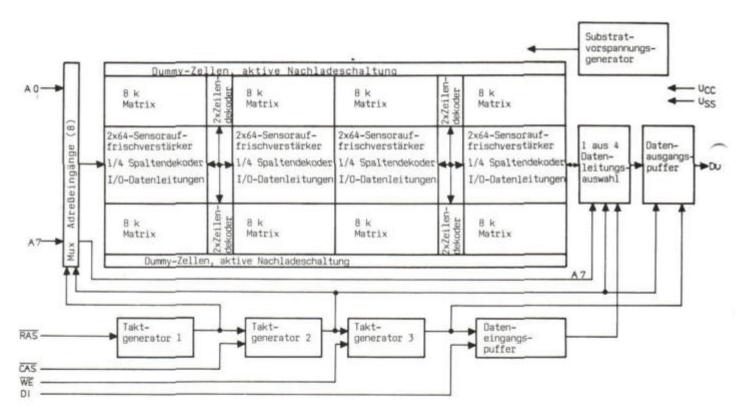

Bild 3: Blockschaltbild

#### Funktionsweise

#### Adressierung

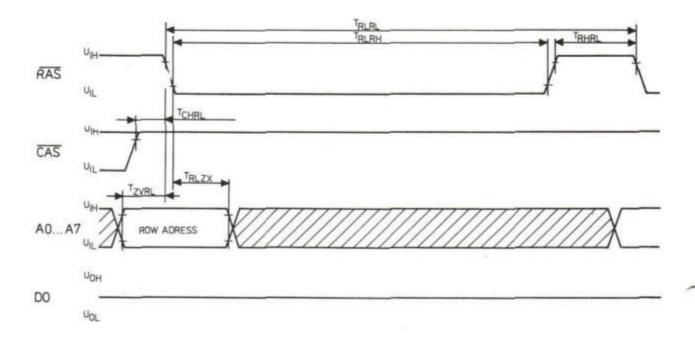

Die 16 Adressen, die zur Auswahl einer der 65 536 Speicherzellen erforderlich sind, werden zeitmultiplex über die 8 Adresseneingänge A D ... A 7 in die internen Adressenspeicher übernommen. Das wird durch die zeitliche Folge zweier abfallender Flanken von Taktimpulsen mit TTL-Pegeln erreicht.

Der erste Taktimpuls, Row-Adress-Strobe (RAS), übernimmt die Reihenadressen in den Chip. Der zweite Taktimpuls, Column-Adress-Strobe (CAS), übernimmt danach die 8 Spaltenadressen in den Chip. Jedes dieser Signale RAS und CAS löst eine Folge von intern erzeugten Taktimpulsen aus.

Die beiden Taktketten sind logisch in der Weise gegeneinander verriegelt, daß die zeitmultiplexe Adressenübernahme außerhalb des kritischen Zeitweges für den Datenzugriff beim Lesen liegt. Die späteren Ereignisse in der CAS-gesteuerten Taktkette sind gesperrt, bis ein Signal (GATEO CAS) entsteht, das von der RAS-Taktkette abgeleitet ist. Dieses GATEO CAS erlaubt, daß der CAS-Takt extern dann schon aktiviert werden darf, wenn die Zeilenadressenhaltezeit (T<sub>RLZX</sub>) vergangen ist und die Adresseninformation von Zeile zu Spalte gewechselt hat.

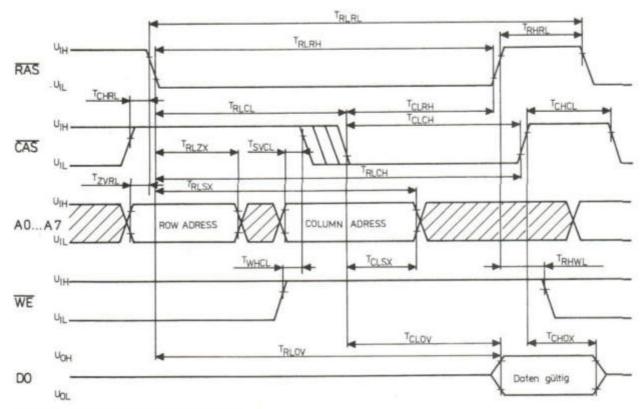

#### Datenein- und -ausgang

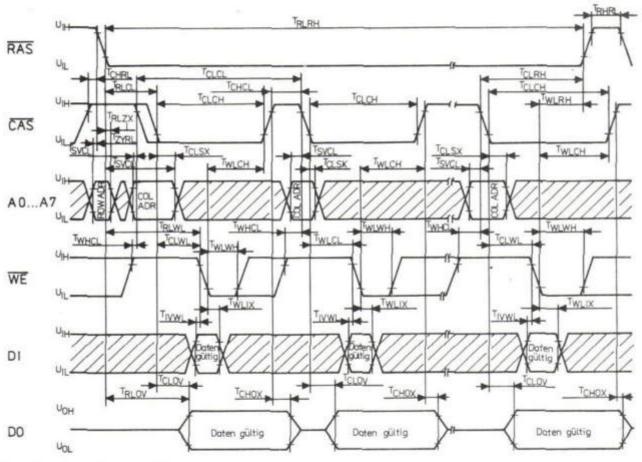

Die Baten, die in eine ausgewählte Zelle eingeschrieben werden sollen, werden bei einer Kombination der WE- und CAS-Signale in ein Dateneingangsregister übernommen, wenn RAS aktiv ist. Das letzte der beiden Signale (WE, CAS) veranlaßt mit seiner abfallenden Flanke die Übernahme der Dateninformation (DI) in das Dateneingangsregister; dadurch gibt es verschiedene Möglichkeiten der Schreibzyklussteuerung.

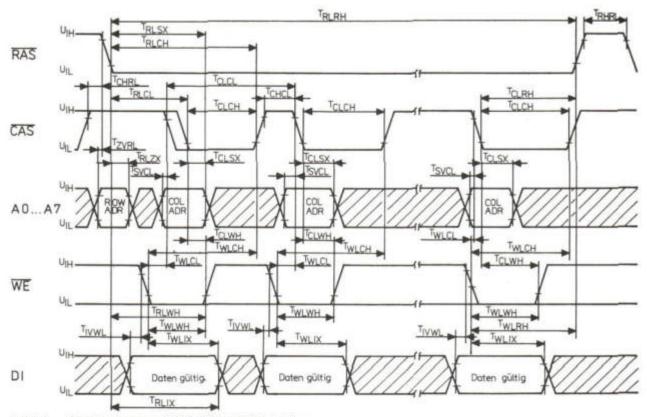

Bei einem Schreibzyklus, bei dem  $\overline{\text{WE}}$  vor  $\overline{\text{CAS}}$  aktiv (Low) wird, wird DI durch  $\overline{\text{CAS}}$  übernommen. Die Dateneingangsvorhaltezeit (T $_{\text{IVCL}}$ ) und -haltezeit (T $_{\text{CLIX}}$ ) sind dann auf  $\overline{\text{CAS}}$  zu beziehen.

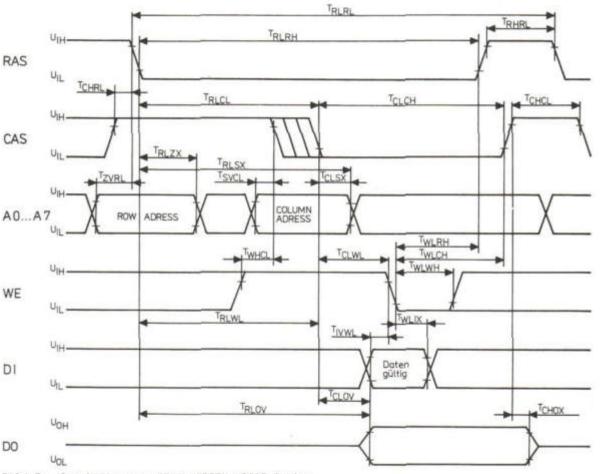

Wenn die Eingangsdaten beim CAS-Übergang noch nicht verfügbar sind oder wenn ein READ-WRITE-Zyklus gewünscht wird, muß das WE-Signal verzögert werden bis der CAS-Übergang erfolgte.

In diesem DELAYED-WRITE-Zyklus sind die o. g. Zeiten ( $T_{IVWL}$  bzw.  $T_{WLIX}$ ) auf WE zu beziehen (sh. Bild 4 und 7).

#### Datenausgangssteuerung

Der normale Zustand des Datenausganges (DO) ist der hochohmige Zustand. Immer wenn  $\overline{\text{CAS}}$  inaktiv (High) ist, ist DO im hochohmigen Zustand. Der einzige Zeitpunkt, in dem der Ausgang eingeschaltet ist und die logische O oder 1 enthält, ist nach der Zugriffszeit bei einem Lesezyklus. DO ist dann gültig, bis  $\overline{\text{CAS}}$  zurück in den inaktiven (High-) Zustand geht.

Wenn der Speicherzyklus ein READ-, READ-MODIFY-WRITE- oder ein DELAYED-WRITE-Zyklus ist, dann geht DO vom hochohmigen in den aktiven Zustand über. Nach der Zugriffszeit steht der Inhalt der ausgewählten Zelle (nicht invertiert zum ehemaligen DI-Signal) zur Verfügung. Der Ausgang bleibt aktiv, bis CAS inaktiv (High) wird, unabhängig davon, ob RAS inaktiv wird oder nicht.

Wenn der Speicherzyklus ein WRITE-Zyklus ist (WE aktiv, bevor CAS aktiv wird), dann behält der Datenausgang DO seinen hochohmigen Zustand während des gesamten Zyklusses. Diese Konfiguration erlaubt dem Anwender volle Steuermöglichkeit von DO allein durch die Zeitsteuerung von WE. Dadurch, daß der Ausgang die Daten speichert, bleiben die Daten von der Zugriffszeit an bis zum Beginn eines folgenden Zyklusses ohne Nachteil für die Zugriffszeit (Ausdehnung) gültig.

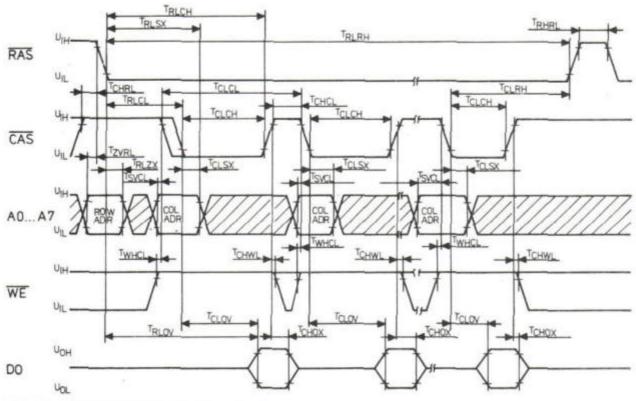

#### PAGE-MODE

Die PAGE-MODE-Zyklen erlauben bei aufeinanderfolgende Speicheroperationen für verschiedene Spaltenadressen bei der gleichen Zeilenadresse erhöhte Geschwindigkeit ohne Anwachsen der Verlustleistung. Das wird durch eine eingespeicherte Zeilenadresse und RAS = aktiv (Low) während aller folgenden Speicherzyklen, die sich auf die gleiche Zeilenadresse beziehen, erreicht. Dieser PAGE-MODE-Zyklus spart die Verlustleistung ein, die mit dem RAS-Übergang verbunden ist. Die Zeit für die Übernahme weiterer Zeilenadressen wird dann eingespart. Deshalb sind Zugriffs- und Zykluszeit um diesen Betrag kleiner.

#### Auffrischen

Das Auffrischen der Daten in der Speichermatrix mit dynamischen Zellen wird ausgeführt, indem ein Speicherzyklus für jede der 128 (A O ... A 6) Zeilenadressen in dem Zeitintervall von 2 ms ausgeführt wird.

Neben den normalen Speicherzyklen ist dies auch mittels RAS-ONLY-REFRESH-Zyklen vorteilhaft möglich. Damit ergibt sich eine erheblich niedrigere Verlustleistung.

#### Einschalten der Betriebsspannungen

Solange eine beliebige Eingangsspannung nicht negativer als -0,3 V ist, wird keine bestimmte Reihenfolge der Signale vorgeschrieben. Eingangsspannungen negativer als -0,3 V dürfen an den Eingangsanschlüssen erst 1 ms nach dem Anlegen der Betriebsspannung auftreten.

Wenn im Fehlerfall die Versorgungsspannung die angegebene Grenze überschreitet, sind zur Vermeidung von Ausfällen die Signale  $\overline{\text{RAS}}$  und  $\overline{\text{CAS}}$  in den inaktiven Zustand zu steuern.

Nachdem die Betriebsspannungen anliegen, benötigt der Speicher mindestens 8 REFRESH-Zyklen, um seinen normalen Betrieb zu gewährleisten.

#### Grenzwerte (USS = 0 V)

| Kennwert                    | Kurzzeichen     | U 2164 D 20/ | Einheit |    |  |

|-----------------------------|-----------------|--------------|---------|----|--|

|                             |                 | min.         | max.    |    |  |

|                             |                 |              |         |    |  |

| Spannung an allen Eingängen | U <sub>T</sub>  | -2,0         | 7,0     | V  |  |

| Ausgangsspannung            | U <sub>O</sub>  | -2,0         | 7,0     | V  |  |

| Betriebsspannung            | u <sub>cc</sub> | -0,5         | 7,0     | V  |  |

| Betriebstemperatur          | ∂ <sub>2</sub>  | 0            | 70      | *C |  |

| Lagerungstemperatur         | ∂stg            | -65          | 150     | *C |  |

| Verlustleistung             | Pu              |              | 1       | W  |  |

#### Betriebsbedingungen (Die Zeitmessung erfolgt mit $t_T = 5$ ns.)

| Kennwert                                       | Kurz-            | U 2164 D 20 |       | U 2164 D 25 |      | Ein- | Bedin- |

|------------------------------------------------|------------------|-------------|-------|-------------|------|------|--------|

|                                                | zeichen          | min.        | max.  | min.        | max. | heit | gungen |

| Betriebsspannung                               | UCC              | 4,5         | 5,5   | 4,75        | 5,25 | v    |        |

| Eingangsspannung High                          | UIH              | 2,4         | 5,5   | 2,4         | 5,5  | V    |        |

| Eingangsspannung Low                           | UIL              | -2,0        | 0,8   | -2,0        | 0,8  | V    | 1)     |

| Übergangszeit (Anstieg/Abfall)                 | tT               | 3           | 50    | 3           | 50   | ns   | 2)     |

| RAS-Vorladezeit                                | TRHRL            | 120         |       | 200         |      | ns   | 3)     |

| RAS-Haltezeit                                  | TCLRH            | 110         | 1     | 150         |      | ns   | 100    |

| CAS-Haltezeit                                  | TRLCH            | 200         |       | 250         |      | ns   |        |

| RAS-CAS-Verzögerungszeit                       | TRLCL            | 45          | 90    | 75          | 100  | ns   | 1      |

| CAS-Vorladezeit                                | TCHCL            | 45          | 10000 | 90          |      | ns   |        |

| CAS-RAS-Vorladezeit                            | TCHRL            | -20         |       | -20         |      | ns   |        |

| Zeilenadressenvorhaltezeit                     | TZVRL            | 0           |       | 0           |      | ns   | 1      |

| Zeilenadressenhaltezeit                        | TRLZX            | 30          |       | 45          |      | ns   |        |

| Spaltenadressenvorhaltezeit                    | TSVCL            | 0           |       | 0           |      | ns   |        |

| Spaltenadressenhaltezeit                       | Toron            | 45          |       | 60          |      | ns   |        |

| Spaltenadressenhaltezeit von RAS <sub>an</sub> | TRUSK            | 135         |       | 160         |      | ns   | 1      |

| Refresh-Periode                                | t <sub>REF</sub> |             | 2     |             | 2    | ms   |        |

| Kennwert                          | Kurz-             | U 2164 D 20 |       | U 2164 D 25 |        | Ein- | Bedin- |

|-----------------------------------|-------------------|-------------|-------|-------------|--------|------|--------|

|                                   | zeichen           | min.        | max.  | min.        | max.   | heit | gunger |

| READ/WRITE-Zyklus                 |                   |             |       |             |        |      |        |

| Zykluszeit                        | TRUBL             | 330         |       | 460         |        | ns   |        |

| RAS-Impulsbreite                  | TRLRH             | 200         | 10000 | 250         | 10000  | ns   |        |

| CAS-Impulsbreite                  | TCLCH             | 110         | 10000 | 150         | 10000  | ns   |        |

| Lesekommandovorhaltezeit          | TWHCL             | 0           |       | 0           |        | ns   |        |

| Lesekommandohaltezeit             | T <sub>RHWL</sub> | 0           | 1     | 0           | 1      | ns   | 1      |

| WE-Vorhaltezeit                   | TWLCL             | 0           |       | 0           | 1      | ns   | 4)     |

| WE-Haltezeit                      | TCLWH             | 40          |       | 50          |        | ns   | 1000   |

| WE-Haltezeit von RAS an           | TRLWH             | 130         |       | 150         |        | ns   |        |

| WE-Impulsbreite                   | TWLWH             | 45          |       | 50          |        | ns   |        |

| WE-RAS-Vorhaltezeit               | TWLRH             | 55          |       | 60          |        | ns   |        |

| WE-CAS-Vorhaltezeit               | TWLCH             | 55          |       | 60          |        | ns   |        |

| Dateneingangsvorhaltezeit         | TIVCL             | 0           |       | 0           |        | ns   | 5)     |

|                                   | TIVUL.            |             |       | 1           |        |      |        |

| Dateneingangshaltezeit            | TCLIX             | 45          |       | 60          |        | ns   | 5)     |

|                                   | TWLIX             | 1300        |       |             |        |      |        |

| Dateneingangshaltezeit von RAS an | TRLIX             | 135         |       | 160         |        | ns   |        |

| SHIPP STANDARD SANDARD SANDARD    | RLIX              | - 1000      |       |             |        | 1.00 |        |

| READ-MODIFY-WRITE-Zyklus          |                   |             |       |             |        |      |        |

| RW-Zykluszeit bei RMW             | TRLRL             | 375         |       | 495         |        | ns   |        |

| RAS-Impulsbreite bei RMW          | TRLRH             | 230         | 10000 | 285         | 10000  | ns   |        |

| CAS-Impulsbreite bei RMW          | TCLCH             | 140         | 10000 | 185         | 10000  | ns   | 1      |

| RAS-WE-Verzögerungszeit           | TRLWL             | 175         |       | 220         |        | ns   | 4)     |

| CAS-WE-Verzögerungszeit           | TCLWL             | 85          |       | 120         |        | ns   | 4)     |

| PAGE-MODE-Zyklus                  | GENE              |             |       |             |        |      |        |

| RW-Zykluszeit im PGM              | TCLCL             | 200         |       | 280         |        | ns   |        |

| RMW-Zykluszeit im PGM             | TRLRH             | 230         |       | 325         |        | ns   |        |

| CAS-Vorladezeit im PGM            | TCLCH             | 80          |       | 128         | 1      | ns   |        |

| RAS-Impulsbreite im PGM           | TCHWL             | 200         | 10000 | 300         | 10000  | ns   |        |

| CAS-Impulsbreite im PGM           | TCHCL             | 110         | 10000 | 150         | 10000  | ns   |        |

| Lesekommandohaltezeit im PGM      | TCLCL             | 0           |       | 0           | 100000 | ns   |        |

#### Bedingungen

- Die Eingangsspannung Low darf nicht länger als 40 ns negativer als -0.3 V sein.

- $\mathbf{U}_{\mathrm{IHmin}}$  und  $\mathbf{U}_{\mathrm{ILmax}}$  sind Bezugspunkte für die Zeitmessung der Eingangssignale, Übergangszeiten werden zwischen  $U_{\mathrm{IH}}$  und  $U_{\mathrm{IL}}$  gemessen.

- 3) Betrieb innerhalb  $T_{RLCL}$  sichert, daß  $T_{RLOV}$  max. eingehalten wird  $(T_{RLCLmax}$  ist nur als

- Bezugspunkt angegeben.). Wenn  $T_{RLCL} > T_{RLCLmax}$ , dann wird die Zugriffszeit  $T_{RLOV}$  verlängert. 4)  $T_{WLVL}$ ,  $T_{RLWL}$  und  $T_{CLWL}$  sind keine einschränkenden Betriebsparameter. Wenn  $T_{WLCL} \geq T_{WLCLmin}$ , ist der Zyklus ein EARLY-WRITE-Zyklus und der Datenausgang bleibt während des gesamten CAS-Zyklusses hochohmig. Wenn  $T_{CLWL} = T_{CLWLmin}$  und  $T_{RLWL} = T_{RLWLmin}$ , ist der Zyklus ein READ-WRITE-Zyklus und der Datenausgang gibt die Information der gelesenen Zelle ab. Wenn keine dieser Bedingungen erfüllt ist, ist der Zustand des Datenausganges zur Zugriffszeit unbestimmt.

- 5) Diese Parameter beziehen sich auf CAS in EARLY-WRITE- und auf WE in DELAYED-WRITE- bzw. READ-MODIFY-WRITE-Zyklen.

- 6) Der Ausgang ist abgeschaltet (hochohmig), RAS und CAS sind High (logisch 1).

- Annahme, daß T<sub>RLCL</sub> = T<sub>RLCLmax</sub>

- gemessen mit 2 TTL-Lasten, 100 pF 8)

- 9) T<sub>CHOXmax</sub> definiert die Zeit, zu welcher der Datenausgang hochohmig wird, diese Zeit ist nicht auf einen Pegel bezogen.

#### Statische Kennwerte

| Kennwert                                                             | Kurz-            | U 2164 D 20 |      | U 2164 D 25 |      | Ein- | Bedingung                                         |

|----------------------------------------------------------------------|------------------|-------------|------|-------------|------|------|---------------------------------------------------|

|                                                                      | zeichen          | min.        | max. | min.        | max. | heit | V-10-0-11-10-11                                   |

| Betriebsstrom (mittlerer Wert<br>bei RAS-CAS-Zyklen)                 | I <sub>001</sub> |             | 55   |             | 55   | mA   | IRLRL*IRLRLmi<br>Sa = 25 °C                       |

| Ruhestrom                                                            | I <sub>002</sub> |             | 5    |             | 5    | mA   | RAS = U <sub>IH</sub><br>DO = High Z              |

| Refreshstrom (mittlerer Wert)                                        | I <sub>DD3</sub> |             | 40   |             | 40   | mA   | TRLEL =TRLELMIN                                   |

| PAGE-MODE-Strom<br>(mittlerer Wert)                                  | I <sub>DD4</sub> |             | 40   |             | 40   | mA   | RAS = UIL<br>ICLCL=ICLCLmi                        |

| Eingangsleckstrom<br>(beliebiger Eingang, alle<br>anderen Pins: O V) | ı                | -10         | 10   | -10         | 10   | μА   | ϑ <sub>a</sub> = 25 °C<br>U <sub>0</sub> = 05,5 V |

| Ausgangsleckstrom<br>(DD = High Z)                                   | I <sub>C</sub>   | -10         | 10   | -10         | 10   | μА   | U <sub>0</sub> =05,5 v <sup>6</sup>               |

| Ausgangsspannung H                                                   | UDH              | 2,4         |      | 2,4         |      | V    | $I_{OUT} = -4 \text{ mA}$                         |

| Ausgangsspannung L                                                   | UOL              |             | 0,4  |             | 0,4  | V    | $I_{cust} = 4 \text{ mA}$                         |

| Eingangskapazität<br>(A O A 7, DI)                                   | c <sub>I</sub>   |             | 6    |             | 6    | pF   | ∂ = 25 °C                                         |

| Eingangskapazität<br>(RAS, CAS, WE)                                  | C,               |             | 8    |             | 8    | pF   | ∂ = 25 °C                                         |

| Ausgangskapazität                                                    | C <sub>D</sub>   |             | 7    |             | 7    | pF   | CAS = UTH                                         |

#### Dynamische Kennwerte

| Kennwert                                                     | Kurz-<br>zeichen                                            | U 2164 D 20 |                    | U 2164 D 25 |                  | Ein-     | Bedingung                 |

|--------------------------------------------------------------|-------------------------------------------------------------|-------------|--------------------|-------------|------------------|----------|---------------------------|

|                                                              |                                                             | min.        | max.               | min.        | max.             | heit     |                           |

| RAS-Zugriffszeit<br>CAS-Zugriffszeit<br>Ausgangsabschaltzeit | T <sub>RLOV</sub><br>T <sub>CLOV</sub><br>T <sub>CHOX</sub> | 0           | 200<br>- 110<br>50 | 0           | 250<br>150<br>50 | ns<br>ns | 7)<br>8)<br>0,5 V über Lo |

|                                                              |                                                             |             |                    | ×           |                  |          | 8,5 V unter<br>High 9)    |

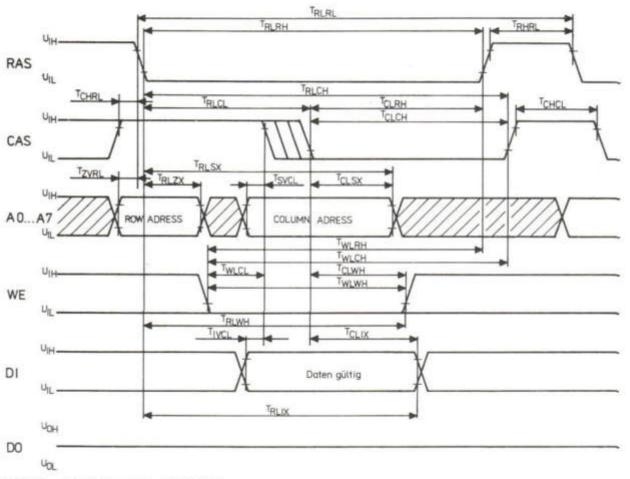

Bild 4: Impulsdiagramm READ-Zyklus

Bild 5: Impulsdiagramm WRITE-Zyklus

Bild 6: Impulsdiagramm PAGE-MODE-WRITE-Zyklus

Bild 7: Impulsdiagramm READ-MODIFY-WRITE-Zyklus

Bild 8: Impulsdiagramm PAGE-MODE-REAU-Zvklus

Bild 9: Impulsdiagramm PAGE-MODE-READ-MODIFY-WRITE-Zyklus

Bild 10: Impulsdiagramm RAS-ONLY-REFRESH-Zyklus

Dieses Datenblatt gibt keine Auskunft über Liefermöglichkeiten und beinhaltet keine Verbindlichkeiten zur Produktion. Die gültige Vertragsunterlage beim Bezug der Bauelemente ist der Typstandard. Rechtsverbindlich ist jeweils die Auftragsbestätigung.

Änderungen im Zuge der technischen Weiterentwicklung vorbehalten.

Die Behandlungsvorschriften für MOS-Bauelemente sind unbedingt einzuhalten, da andernsfalls eine Reklamation nicht anerkannt werden kann.

11/87

### veb mikroelektronik karl marx erfurt stammbetrieb

DDR-5023 Erfurt, Rudolfstraße 47 Telefon 5 80, Telex 061 306

Volkseigener Außenhandelsbetrieb der Deutschen Demokratischen Republik DDR ~ 1026 Berlin, Alexanderplatz 6 Telex: BLN 114721 elei. Telefon: 2180