1-Megabitspeicherschaltkreis, dynamisch

## Kurzcharakteristik

- Dynamischer Schreib-/Lesespeicher mit wahlfreiem Zugriff

- Speicherorganisation: 1.048.576 × 1 Bit

- Hohe Arbeitsgeschwindigkeit, geringe Verlustleistung

- TTL- und CMOS-Kompatibilität der Ein- und Ausgänge

- Tristate-Ausgangsstufen

- Betriebsspannung: 5V ± 10 %

- 512 Refreshzyklen; Refreshzeit 8 ms

- Betriebs- und Refresharten:

READ CYCLE

EARLY WRITE CYCLE

- READ-WRITE CYCLE

FAST PAGE MODE (READ und WRITE)

FAST PAGE READ-WRITE

RAS ONLY REFRESH

CAS BEFORE RAS REFRESH

HIDDEN REFRESH (READ und WRITE)

CAS BEFORE RAS COUNTER TEST

- Gehäuse: 18polig DIP (Bauform A1HA nach TGL 26713/02), Gehäuse in Aufsetztechnik (SOJ) in Vorbereitung

- Kompatibel zu internationalen

Vergleichstypen, z. B.

TC 511000 (Toshiba)

HYB 511000 (Siemens)

#### Hinweis:

Im Übergangszeitraum kann als Gehäuse auch ein 18poliges Keramik-DIP-Gehäuse zum Einsatz kommen. In diesem Fall lauten die Typenbezeichnungen

U 61000 CC12 und U 61000 CC10.

Änderungen im Interesse des technischen Fortschritts vorbehalten.

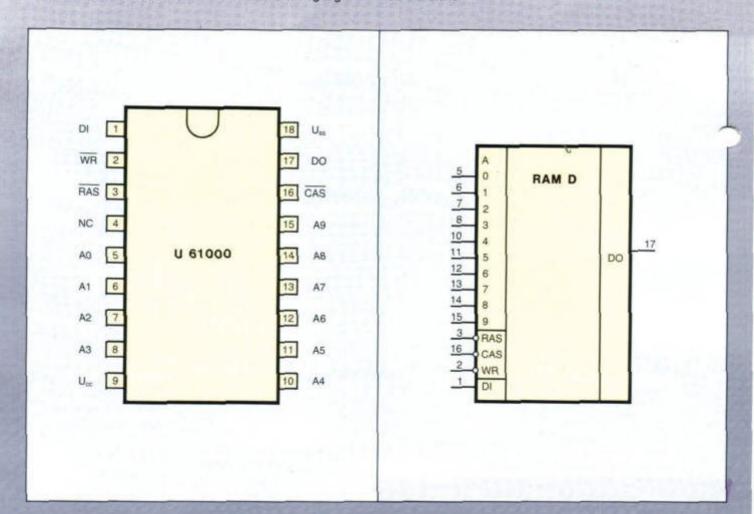

# Anschlußbelegung und Schaltzeichen

A0...A9 Adreßeingänge

DI DO RAS

CAS

Dateneingang Datenausgang Zeilenadreßstrobe

Spaltenadreßstrobe

WR

Schreib-/Lesesteuerung

Use

Betriebsspannung Masse

Uss

Anschlußbelegung

Schaltzeichen

#### **Allgemeines**

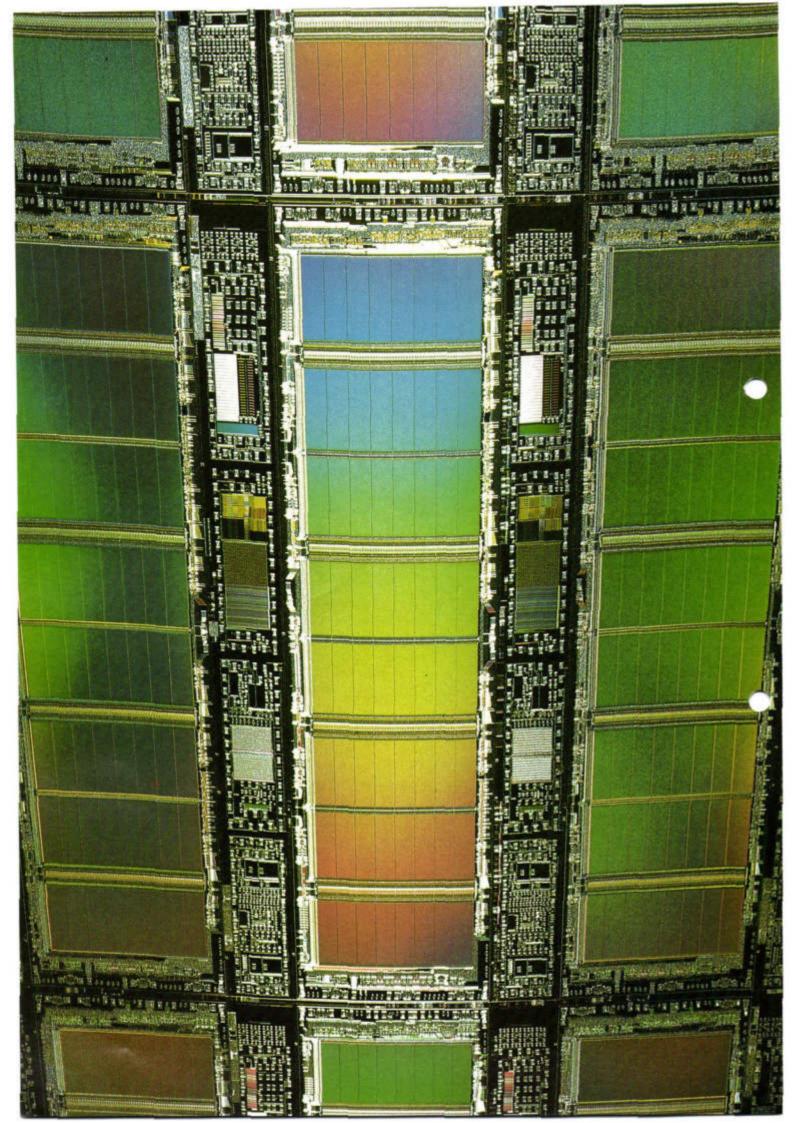

Der dynamische 1-Megabit-Schreib-/ Lese-Speicher U 61000 ist der erste Schaltkreistyp unserer Fertigung auf Basis einer n-Wannen-CMOS-Technologie im Strukturniveau 1 μm.

Dieses Strukturniveau, die Anwendung von 4 Leitbahnebenen (2 x Polysilizium und je 1 x Molybdänsilicid und Aluminium) sowie die Ein-Transistor-Speicherzelle erläuben eine sehr hohe Pakkungsdichte, so daß der Chip in kleine Standardgehäuse montiert werden kann

Der U 61000 besitzt die Organisation 1 M × 1 Bit und arbeitet im Fast Page Mode (FPM).

Eine Weiterentwicklung auf Basis des gleichen Chips ist möglich

B. Static Column Mode, Organisation & K × 4 Bit). Der Schaltkreis U 61000 ist vorwiegend für den Einsatz in der Rechen- und Nachrichtentechnik und in der Industrieelektronik vorgesehen. Technologische und entwurfsseitige Maßnahmen gegen "Softerrors", den "Latch-up-Effekt" und die elektrostatische Empfindlichkeit der Eingänge sind getroffen.

## Vorläufige technische Daten

|                          | U 61000 DC12<br>Grundtyp | U 61000 DC10<br>Selektionstyp |

|--------------------------|--------------------------|-------------------------------|

| RAS-Zugriffszeit         | 120 ns                   | 100 ns                        |

| CAS-Zugriffszeit         | 45 ns                    | 35 ns                         |

| FPM-Zugriffszeit         | 60 ns                    | 50 ns                         |

| Zykluszeit               | 220 ns                   | 190 ns                        |

| FPM-Zykluszeit           | 70 ns                    | 55 ns                         |

| Betriebsspannung         | 4,5 5,5 V                |                               |

| Betriebsstrom            | max. 50 mA               | max. 60 mA                    |

| Ruhestrom bei CMOS-Pegel | max. 1 mA                |                               |

| bei TTL-Pegel            | max. 2 mA                |                               |

| Betriebstemperatur       | 070°C                    |                               |

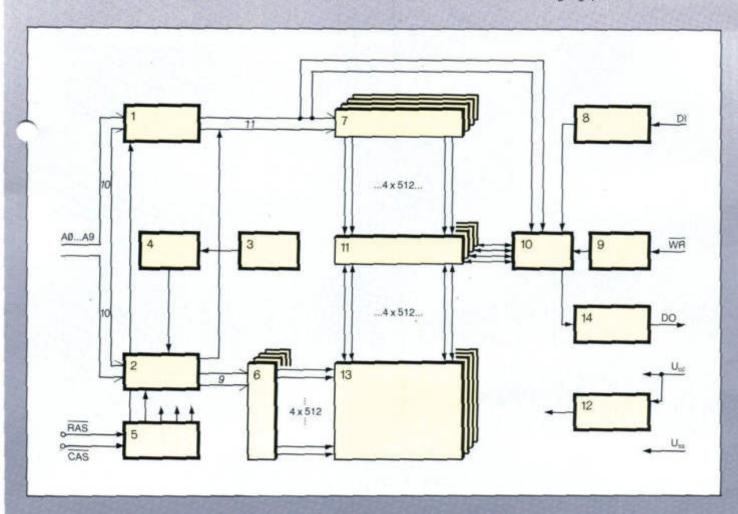

### Blockschaltbild 1 MdRAM U 61000

- 1 Spaltenadreßpuffer

- 2 Zeilenadreßpuffer

- 3 Refreshsteuerung

- 4 Interner Adre8zähler

- 5 Interner Taktgenerator

- 6 Zellendekoder

- 7 Spaltendekoder

- 8 Eingangsputter

- 9 Schreib-/Lesesteuerung

- 10 I/O-Selektor

- 11 Sensorverstärker

- 12 Substratspannungsgenerator

- 13 Speichermatrix (4 x 256 k Zellen)

- 14 Ausgangspuffer

VEB Forschungszentrum Mikroelektronik Dresden Betrieb des Kombinates VEB Carl Zeiss JENA

Carl-Zeiss-Straße 1 Jena DDR-6900

Kurzprospekt Ausgabe 02/89 (vorl. techn. Daten) AG: 203-650/90009