# Information

# U 736 DC

## CMOS — 31/2-Digit-Analog-Digital-Wandler

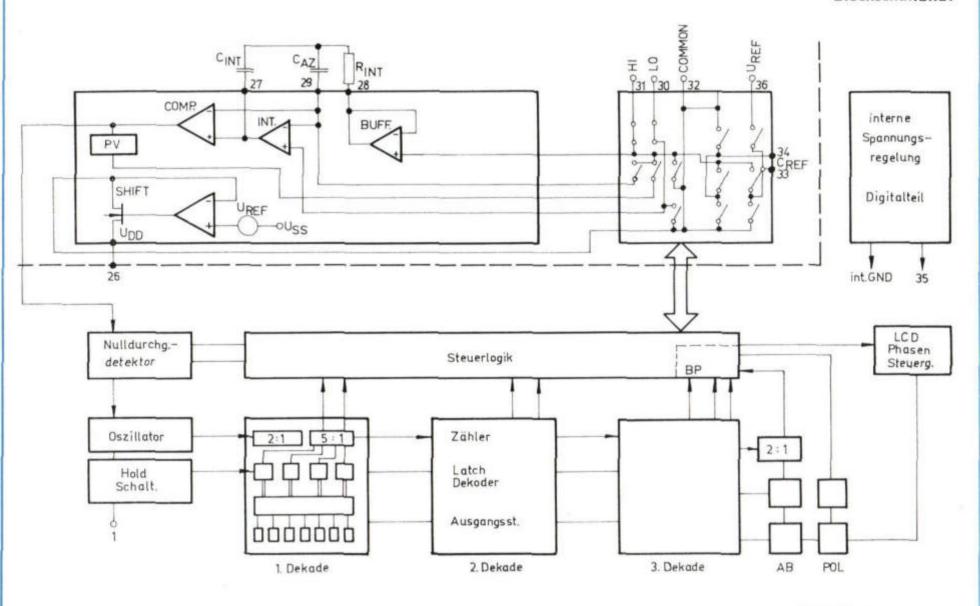

Der U 736 DC ist ein monolithisch integrierter vollständiger 3 1/2-Digit-Analog-Digital-Wandler mit Hold-Betrieb nach dem Zweiflankenverfahren mit automatischem Nullpunktabgleich in CMOS-Technik.

Auf dem Chip sind folgende Schaltungsteile integriert:

- Analogschalternetzwerk

- Referenzspannungserzeugung

- Digitalteil mit Steuerwerk, Zähler, Latch, Dekoder und LCD-Ausgangsstufen

- Taktgenerator und Taktimpulsaufbereitung

Der U 736 DC zeichnet sich insbesondere durch seine geringe Stromaufnahme, seine geringe Außenbeschaltung und den Betrieb aus nur einer Betriebsspannung aus.

Der U 736 DC kann direkt eine Flüssigkristallanzeige für Parallelansteuerung (z. B. FAR 09) treiben.

Der Hold-Anschluß dient zum Stoppen der Aufdatierung des Anzeigespeichers, so daß ein Ablesen des zuletzt eingelesenen Wertes möglich wird.

#### Vorläufige technische Daten:

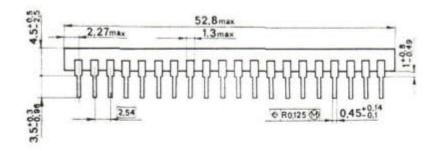

Gehäuse: 40polig DIL-Plast

Rastermaß: 2.54 mm

Bauform: A1 OF nach TGL 26713/02

Reihenabstand: 15,24 mm

A1 OF TGL 26713 / 02

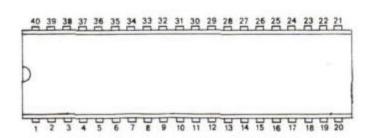

## Anschlußbelegung:

| 1  | Hold     | 21 | BP     |

|----|----------|----|--------|

| 2  |          | 22 |        |

| 3  |          |    | 100 G  |

|    |          | 23 | 100 A  |

| 4  | 1 B      | 24 | 100 C  |

| 5  | 1 A      | 25 | 10 G   |

| 6  | 1 F      | 26 | UDD    |

| 7  | 1 G      | 27 | CINT   |

| 8  | 1 E      | 28 | BUFF   |

| 9  | 10 D     | 29 | CA/Z   |

| 10 | 10 C     | 30 | INLD   |

| 11 | 10 B     | 31 | INHI   |

| 12 | 10 A     | 32 | COMMON |

| 13 | 10 F     | 33 | CREF-  |

| 14 | 10 E     | 34 | CREF+  |

| 15 | 100 D    | 35 | USS    |

| 16 | 100 B    | 36 | REFHI  |

| 17 | 100 F    | 37 | TEST   |

| 18 | 100 E    | 38 | OSC 3  |

| 19 | 1.000 AB | 39 | OSC 2  |

| 20 | POL      | 40 | OSC 1  |

|    |          |    |        |

Ein Einsatz des U 736 DC auf 2,5 mm Raster ist nicht zulässig

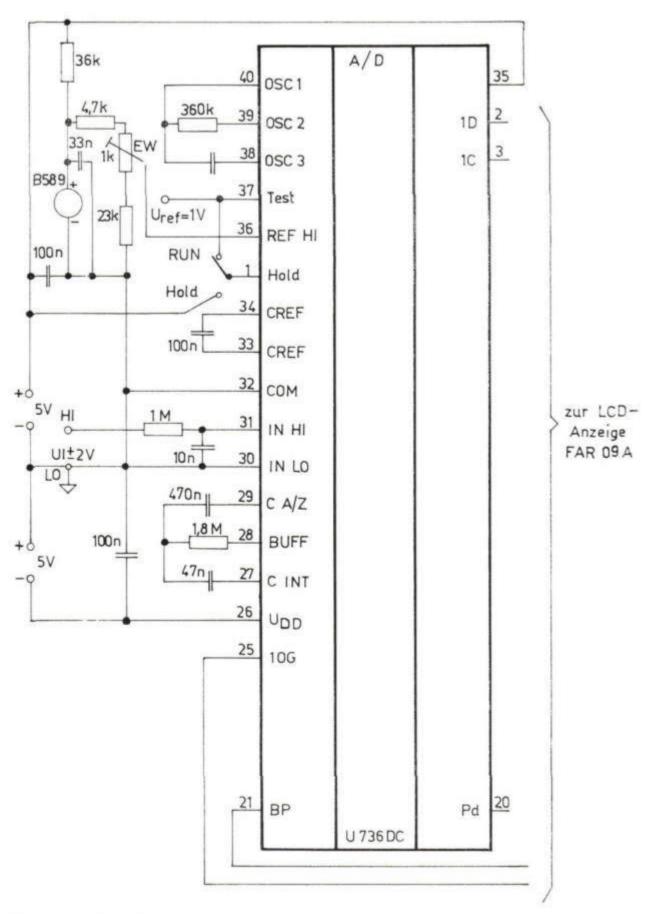

## Blockschaltbild:

U 736 A1188

| Grenzwerte:                                       |                                     | min.              | typ. | max. |   |

|---------------------------------------------------|-------------------------------------|-------------------|------|------|---|

| Betriebsspannung (gegen U <sub>DD</sub> )         | U <sub>SS</sub>                     | 0                 | _    | +15  | V |

| Analogeingangsspannungen                          | U <sub>130</sub> ; U <sub>131</sub> | Uup               | _    | Uss  | V |

| Eingangsspannung bei externer<br>Taktung an OSC 1 | U <sub>140</sub>                    | U <sub>Test</sub> | -    | Uss  | ٧ |

Der Eingangsspannungsbereich darf an INHI und INLO bei Begrenzung des Eingangsstromes auf  ${\le}100~\mu\text{A}$  überschritten werden.

| Betriebsbedingungen:    |              | min. | typ. | max. |         |

|-------------------------|--------------|------|------|------|---------|

| Betriebsspannung        | Uss          | -    | 9    | -    | ٧       |

| Bufferungsausgangsstrom | lobuff       | -    | _    | 1    | $\mu A$ |

| Umgebungstemperatur     | $T_{\alpha}$ | 0    | 25   | 70   | °C      |

| Taktfrequenz            | fosz         | -    | 50   | 64   | kHz     |

**Kenngrößen,** gültig bei  $U_{DD}=9$  V;  $U_{REF}=1$  V;  $f_{OSZ}=50$  kHz;  $T_{\sigma}=25$  °C — 5 K, falls nicht anders angegeben

| Stromaufnahme                                                            | Iss             |     |      |      |       |

|--------------------------------------------------------------------------|-----------------|-----|------|------|-------|

| $U_{SS} = 15 \text{ V}$                                                  |                 | -   | 100  | 200  | μА    |

| Linearitätsfehler                                                        | EL              | —1  | _    | +1   | Digit |

| Segment- und<br>Backplaneausgangsspannung                                | Uosg/Uobp       | 4   | -    | 6    | ٧     |

| Umpolfehler $U_{REH} = 100 \text{ mV};$ $U_{IN} = \text{ca. I 190 mV I}$ | E <sub>RO</sub> | _1  | -    | +1   | Digit |

| Ratiomessung (Display) $U_{IE} = U_{REF} = 100 \text{ mV}$               | R <sub>RR</sub> | 999 | 1000 | 1001 |       |

| Common-Spannung gegen U <sub>SS</sub> ; I <sub>COM</sub> = 10 µA         | —Исом           | 2,6 | _    | 3,4  | ٧     |

| TK der Common-Spannung                                                   | TKucom          | _   | 150  | _    | ppm/K |

| Nullmessung                                                              | RZ              | _0  | _    | +0   |       |

| Eingangsleckstrom                                                        | I,L             | _   | 1    | _    | pA    |

## Funktionsbeschreibung:

Der U 736 DC arbeitet nach dem Zweiflankenintegrationsverfahren. Während einer zeitlich festen Integrationsphase wird eine der Eingangsspannung proportionale Spannung integriert. In der nachfolgenden Abintegrationsphase erfolgt der Abbau dieser Spannung durch Anlegen einer entsprechend gepolten Referenzspannung. Die Zeitdauer bis zum Nulldurchgang ist der Eingangsspannung proportional, ebenso die Zahl der Taktimpulse während der Abintegration. Diese Taktimpulszahl wird ermittelt. Das angezeigte Ergebnis ist im konkreten Fall

$$1000 \cdot \frac{U_{IN}}{U_{REF}}$$

Der Abintegrationsphase folgt die Nullintegration zum Abbau von vorhandenen Restladungen und danach folgt der automatische Nullabgleich (AUTOZERO).

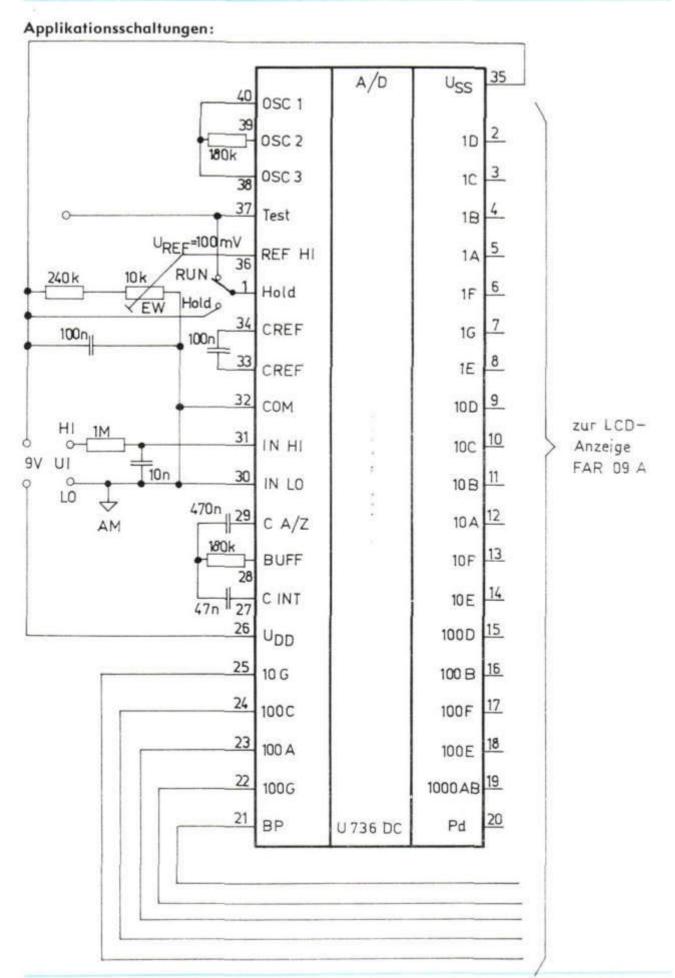

## Außenbeschaltung:

Der U 736 DC wird mit derselben Außenbeschaltung betrieben wie der C 7136 D; zu beachten ist Anschluß 1 = Hold und Anschluß 35 = USS. Der Hold-Anschluß ist ein digitaler Eingang mit einer Schwellspannung, die in der Mitte zwischen USS und TEST liegt. Unabhängig vom Pegel am Hold-Anschluß werden Wandlungen durchgeführt. Liegt der Hold-Anschluß an USS, wird die Aufdatierung des Anzeigespeichers gesperrt. Bei Anlegen von niedrigem Potential erfolgt eine Aufdatierung am Ende eines jeden Wandlungszyklus.

Im Hold-Betrieb wird die niedrigste Verlustleistung erreicht. Der Hold-Anschluß ist CMOSkompatibel und kann mit einem Schalter zwischen TEST und USS betrieben werden. Ein offener Hold-Anschluß wirkt wie Low-Potenial (interner pull down).

Die Referenzspannung kann zwischen REFHI und COMMON angelegt werden.

Versorgung des U 736 DC mit  $\pm 5$  V externe Referenzspannungserzeugung (U<sub>Emax</sub>  $= \pm 2$  V):

veb halbleiterwerk frankfurt/oder im veb kombinat mikroelektronik

Telefon 460 - Telex 016252 Postfach 379 - Frankfurt(Oder) - 1200

## elektronik export-import

Volkseigener Außenhandelsbetrieb der Deutschen Demokratischen Republik DDR - 1026 Berlin, Alexanderplatz 6 Haus der Elektroindustrie, Telefon; 2180