# Information

## Serielle Ein-/Ausgabesteuerung U 82 530 DC / U 8030 DC

Die Serial Communication Controller (serielle Ein-/Ausgabesteuerung) U 82530 DC und U 8030 DC sind programmierbare periphere Schaltkreise in n-Kanal-Silicon-Gate-Technologie. Sie sind entwikkelt worden, um eine umfassende Unterstützung für die Bearbeitung einer Vielzahl serieller Kommunikationsprotokolle zu gewährleisten. Einmal programmiert, entlastet der SCC das Prozessorsystem von Aufgaben, die vorher durch die CPU oder die zugehörige Hardware erfüllt werden mußten.

| Section 1 |                 |                 |                 |

|-----------|-----------------|-----------------|-----------------|

| DB 1 1    | 40 DB 0         | AD 1 1          | 40 AD 0         |

| 0B 3 Z    | 39 DB 2         | AD 3 2          | 39 AD 2         |

| 0B 5 3    | 38 DB 4         | AD 5 3          | 38 AD 4         |

| 08.7 4    | 37 DB 6         | AD 7 4          | 37 AD 6         |

| NT 5      | 36 RD           | INT 5           | 36 DS           |

| EO 6      | 35) WR          | IEO 6           | 35 AS           |

| E) 7      | 34 A/B          | (E) 7           | 34 RIW          |

| NTACK 8   | 33 CE           | INTACK 8        | 33 CS 0         |

| 5 V 9     | 32 D/C          | +5 V g          | 32 CS 1         |

| V/REGA 10 | 31 GND          | W/REQA 10       | 31 GND          |

| YNCA 11   | 30 WREOB        | SYNCA 11        | 30 W/REGB       |

| RT×CA 12  | 29 SYNCE        | RTxCA 12        | 29 SYNCB        |

| EXDA 13   | 28 RT×CB        | RxDA 13         | 28 RTxCB        |

| RxCA 14   | 27 R×DB         | TRXCA 14        | 27 R×DB         |

| x DA 15   | 26 TR×CB        | TXDA 15         | 26 TRXCB        |

| TRI 16    | 25 T×DB         | DTR/<br>REQA 16 | 25 T×DB         |

| ITSA 17   | 24 DTR/<br>REDB | RTSA 17         | 24 DTR/<br>REQB |

| TSA 18    | 23 RTSB         | CTSA 18         | 23 RTSB         |

| XDA 19    | 22 CTS8         | DCDA 19         | 22 CTSB         |

| PCLK ZO   | 21 0008         | PCLK ZO         | 21 0008         |

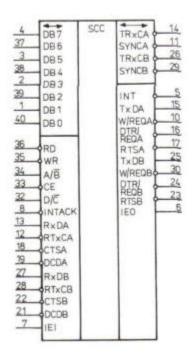

Bild 3: Schaltzeichen U 82530 DC

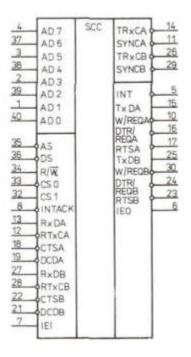

Bild 4: Schaltzeichen U 8030 DC

#### Bezeichnung und Beschreibung der Anschlüsse:

Der SCC ist für Multiplex- (Version U 8030 DC) und Nichtmultiplexbetrieb (Version U 82530 DC) verfügbar. Dementsprechend ist die folgende Pinbeschreibung unterteilt in U 8030 DC-spezifische Pins, U 82530 DC-spezifische Pins und Pins, die für beide Versionen identisch sind. Bild 1 (Bild 3) bezeichnet die Pinanschlüsse und Signalnamen für den U 82530 DC, Bild 2 (Bild 4) die für den U 8030 DC.

#### Pinbeschreibung (nur U 82530 DC)

A/B Auswahl Kanal A/Kanal B (Eingang, Kanal A highaktiv)

Dieses Signal wählt den Kanal aus, in dem der Schreib- oder Lesezyklus ausgeführt

wird

CE Chip Enable (Eingang, lowaktiv)

Signal zur Chipfreigabe

DB 0 ... DB 7 Datenleitungen (bidirektional, tristate)

Anschlußleitungen an den Systemdatenbus

D/C Data/Control (Eingang, Bata highaktiv)

Auswahlsignal: Daten oder Steuerinformation

Read (Eingang, lowaktiv)

Dieses Signal zeigt einen Lesezyklus an und gibt die SCC-Bustreiber frei, falls der SCC ausgewählt wurde. Während eines Interruptanerkennungszyklusses legt dieses Signal den Interruptvektor unter der Voraussetzung auf den Bus, daß der betreffende SCC der Schaltkreis mit der höchsten Priorität in der Interrupt-

Prioritätskette ist, der einen Interrupt anfordert.

WR

Write (Eingang, lowaktiv)

Dieses Signal zeigt einen Schreibzyklus an. Das gleichzeitige Aktivieren von  $\overline{\text{RD}}$  und  $\overline{\text{WR}}$  wird als Hardware-RESET interpretiert.

#### Pinbeschreibung (nur U 8030 DC)

AD 0 ... AD 7 Adre0-/Datenbus (bidirektional, tristate)

Multiplexleitungen zum Anschluß an den Adreß-/Datenbus des Systems

AS Adress Strobe (Eingang, lowaktiv)

Die Adressen auf AD D ... AD 7 werden mit der steigenden Flanke dieses Signals

bewertet.

CS 0 Chip Select 0 (Eingang, lowaktiv)

Dieses Signal wird gleichzeitig mit den Adressen AD 0 ... AD 7 bewertet und muß

aktiv sein, damit der entsprechende Zyklus ablaufen kann.

CS 1 Chip Select 1 (Eingang, highaktiv)

Dieses zweite Auswahlsignal muß ebenfalls aktiv sein, bevor der beabsichtigte

Datentransfer über den Systembus ablaufen kann. CS 1 muß während des Transfers

aktiv bleiben.

DS Data Strobe (Eingang, lowaktiv)

Dieses Signal bestimmt die Zeitsteuerung für den Datentransfer über den System-

bus. Sind  $\overline{\text{AS}}$  und  $\overline{\text{DS}}$  gleichzeitig Low, so wird dies als Hardware-RESET interpre-

tiert.

R/W Read/Write (Eingang, Read highaktiv)

Dieses Signal kennzeichnet den ablaufenden Zyklus als Lese- oder Schreibzyklus.

#### Pinbeschreibung (beide Versionen)

CTSA, CTSB

Clear To Send (Eingänge, lowaktiv)

Wenn diese Pins "Auto Enable" programmiert sind, gibt ein Low an diesen Eingängen den entsprechenden Sender frei. Wenn sie nicht als "Auto Enable" programmiert sind, können sie wahlfrei genutzt werden. Beide Eingänge sind mit Schmitt-Triggern ausgerüstet, um Signale mit einer längeren Anstiegszeit zu verarbeiten. Der SCC erkennt beliebige Pegelwechsel an diesen Eingängen und kann daraufhin

einen Interrupt anfordern.

DCDA, DCDB

Data Carrier Detect (Eingänge, lowaktiv)

Diese Pins sind, wenn sie "Auto Enable" programmiert sind, als Empfängerfreigabe vorgesehen. Andernfalls können sie wahlfrei genutzt werden. Beide Eingänge sind mit Schmitt-Triggern ausgestattet, um Signale mit einer längeren Anstiegszeit zu verarbeiten. Der SCC erkennt beliebige Pegelwechsel an diesen Eingängen und kann

daraufhin einen Interrupt anfordern.

DTR/REQA,

Data Terminal Ready/Request (Ausgänge, lowaktiv)

DTR/REQB

Diese Ausgänge folgen dem Zustand des DTR-Bits. Sie können auch wahlfrei oder als

Anforderungsleitungen für die DMA-Steuerung genutzt werden.

IEI

Interrupt Enable In (Eingang, highaktiv)

Gibt es mehr als einen interruptgesteuerten Schaltkreis im System, wird IEI in Verbindung mit IEO benutzt, um eine Interrupt-Prioritätskette zu realisieren. Ein High an IEI zeigt an, daß momentan für keinen höherpriorisierten Schaltkreis in der Kette ein Interrupt bedient (Interrupt Under Service) oder angefordert

wird.

IEO

Interrupt Enable Out (Ausgang, highaktiv)

IEO ist nur dann high, wenn IEI high ist und die CPU keinen SCC-Interrupt bedient bzw. der SCC keinen Interrupt anfordert. IEO ist mit dem IEI-Eingang des Schaltkreises mit der nächstniedrigeren Priorität verbunden und kann so die Interrupts

der niederpriorisierten Bausteine sperren.

INTACK

Interrupt Acknowledge (Eingang, lowaktiv)

Dieses Signal zeigt einen Interruptanerkennungszyklus an. Während dieses Zyklusses wird die Interrupt-Prioritätskette durchgeschaltet. Wenn  $\overline{\rm OS}$  (U 8030 DC)

bzw.  $\overline{\text{RO}}$  (U 82530 DC)aktiv werden, sendet der SCC einen Interruptvektor auf den Datenbus (falls IEI high ist).  $\overline{\text{INTACK}}$  wird mit der steigenden Flanke von  $\overline{\text{AS}}$  bzw. dem Systemtakt bewertet.

INT

Interrupt Request (open-drain-Ausgang, lowaktiv)

Dieses Signal wird aktiviert, wenn der 500 einen Interrupt anfordert.

C

Systemtakt (Eingang)

Dies ist der Grundtakt, der benutzt wird, um die internen Signale zu synchronisieren. Der Takt am SCC braucht keine feste Phasenbeziehung zum Takt des Prozessorsystems zu haben. Die Frequenz des SCC-Taktes muß jedoch mindestens 90 % der Frequenz des Prozessorsystemtaktes betragen. Der Systemtakt wird mit TTL-Pegel petrieben.

RISA, RISB

Request To Send (Ausgänge, lowaktiv)

Wenn das RTS-Bit in Schreibregister WR 5 gesetzt ist, wird das RTS-Pin Low.

Ist das RTS-Bit im Asynchronbetrieb rückgesetzt, wird Auto Enable eingeschaltet, geht das Signal, nachdem alle Sendespeicher leer sind, auf High-Pegal. Ist im Synchronbetrieb oder im Asynchronbetrieb Auto Enable ausgeschaltet, so folgt das RTS-Pin strikt dem Zustand des RTS-Bits. Beide Pins können wahlfrei genutzt werden.

RIXCA, RIXCB

Empfangs-/Sendetakt (Eingänge, lowaktiv)

Die Funktionen dieser Pins müssen durch den Anwender bestimmt werden. In jedem Kanal kann das RTxC-Pin den Empfangstakt, den Sendetakt, den Takt für den Baud-Rate-Generator oder den Takt für die DPLL liefern. Der Empfangstakt kann im Asynchronbetrieb das 1-, 16-, 32- oder 64fache der Datenrate betragen. Diese Eingänge können in Verbindung mit den entsprechenden SYNC-Pins auch für den Aufbau eines Quarzoszillators genutzt werden.

RxDA, RxD8

Empfangsdatenleitungen (Eingänge, highaktiv)

Diese Empfangssignale empfangen serielle Daten mit Standard-TTL-Pegel.

SYNCA, SYNCB

Synchronislerung (Ein-/Ausgänge, lowaktiv)

Diese Pins können entweder als Eingänge, Ausgänge oder als Teil einer Quarzoszillatorschaltung wirken. Im synchronen Empfangsbetrieb (ohne Quarzoszillator) können diese Pins wie die CT5- und DCD-Pins eingesetzt werden. In dieser Betriebsart beeinflussen Pegelwechsel an diesen Leitungen den Zustand des "Sync/Hunt"-Bits im Leseregister RR D, sie haben dann keine andere Funktion.

Im externen Synchronbetrieb (ohne Quarzoszillator) arbeiten diese Leitungen als Eingänge. In dieser Betriebsart muß SYNC, nachdem das letzte Bit des SYNC-Zeichens empfangen worden ist, über zwei Empfangstaktzyklen aktiviert werden. Die Zeichenübertragung beginnt mit der steigenden Flanke des Empfangstaktes direkt nach der Aktivierung des SYNC-Pins.

Im internen Synchronbetrieb (Monosync und Bisync ohne Quarzoszillator) arbeiten die SYNC-Pins als Ausgänge und sind nur während des Teils des Empfangszyklusses aktiv, in dem SYNC-Zeichen erkannt werden. Die Synchronbedingung wird nicht gespeichert. So sind diese Ausgänge unabhängig von den Zeichenkettengrenzen, immer wenn ein SYNC-Zeichen erkannt wird, aktiv. Im SOLC-Betrieb arbeiten diese Pins als Ausgänge und werden beim Empfang eines SOLC-Flags aktiv.

TRXCA, TRXCB

Sende-/Empfangstakte (Eingänge oder Ausgänge, lowaktiv)

Die Funktion dieser Pins muß durch den Anwender bestimmt werden. Die TRxC-Pins können als Empfangs- bzw. Sendetakteingänge benutzt werden oder die Ausgangssignale der DPLL, des Quarzoszillators, des Baud-Rate-Generators oder den Sendetakt liefern.

TXDA, TXDB

Sendedatenleitungen (Ausgänge, highaktiv)

Diese Ausgänge senden serielle Daten mit ITL-Pegel.

W/REQA,

Wait/Request (Ausgänge, lowaktiv, Wait: open-drain, Request: tristate)

Diese Ausgänge können entweder als Anforderungsleitungen für eine DMA-Steuerung oder als Wait-Leitungen zur Synchronisation des Datentransfers auf den Systembus genutzt werden. Der Zustand des Pins nach RESET entspricht Wait.

4

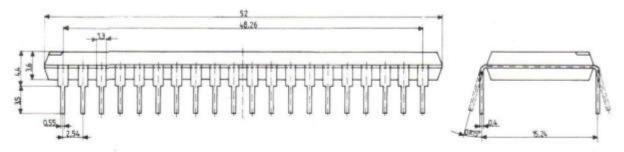

Bild 5: Gehäuseabmessungen

#### Beschreibung

Die Serial Communication Controller (SCC) U 82530 DC und U 8030 DC sind in n-Kanal-Silicon-Gate-Technologie gefertigte, programmierbare, periphere Schaltkreise, die entwickelt worden sind, um umfassende Unterstützung für die Bearbeitung einer Vielzahl serieller Kommunikationsproto-kolle zu gewährleisten. Der SCC kann für spezielle serielle Kommunikationsverfahren eingesetzt werden, aber auch Standardformate wie byteorientierte synchrone, bitorientierte synchrone und asynchrone Formate bearbeiten. Einmal programmiert, entlastet der SCC das Prozessorsystem von Aufgaben, die vorher durch CPU oder die zugehörige Hardware erfüllt werden mußten.

Durch den Zugriff auf 16 Schreibregister und 9 Leseregister pro Kanal kann der Nutzer den SCC so programmieren, daß dieser alle asynchronen Formate ohne Einschränkung in Bezug auf die Anzahl der Datenbits, die Anzahl der Stoppbits oder die Form der Paritätsforderung verarbeitet. Der SCC bearbeitet auch alle synchronen Formate einschließlich zeichen-, byte- und bitorientierter Protokolle.

In allen Betriebsarten ermöglicht der SCC auch Variationen des Übertragungsprotokolls durch Paritätstest, durch Einfügen oder Löschen von Zeichen, CRC-Generierung und -Testung, das Erzeugen und Feststellen von Unterbrechung, Abbruch waw.

Der U 8030 DC wird in Systemen eingesetzt, in denen AdreG- und Datenleitungen im Multiplexbetrieb arbeiten. Der U 82530 DC kann in Mikroprozessorsystemen benutzt werden, in denen AdreG- und Datenleitungen separat vorhanden sind (z. B. U 880 D). Im allgemeinen sind beide Typen jedoch als Schaltkreise innerhalb des Systems der lébit-Leitungsklasse konzipiert.

#### Eigenschaften

- Versorgungsspannung : 5 V · 5 %

- max. Taktfrequenz: 4 MHz (6 MHz in Vorbereitung)

- 4 unabhängige serielle Ports: 2 Sender- und 2 Empfängerports

- synchrone/asynchrone Datenraten:

- \* bis zu i Mbit/sec bei 4 MHz Systemtakt

- \* bis zu 250 kbit/sec bei 4 MHz Systemtakt (FM-Kodierung unter Benutzung der DPLL)

- \* bis zu 125 kbit/sec mit 4 MHz Systemtakt (NRZI-Kodierung unter Benutzung der DPLL)

- alle internen Steuer- und Datenregister sind les- und schreibbar

- Datenregister sind generell direkt adressierbar, Steuerregister nur beim U 8030 DC

- beim U 82530 DC muß auf die Steuerregister mit einer Befehlsfolge zugegriffen werden

- Vektorinterrupt inklusive Status (Ursache), daisy-chain (IEI, IEO) und Polling möglich

- Der WAIT/REQUEST-Ausgang ermöglicht schnelle CPU/DMA-Blockübertragungen, die DTR/REQUEST-Leitung ermöglicht Übertragungen unter DMA-Steuerung in beiden Richtungen (vollduplex)

- Asynchronbetrieb:

- \* 5, 6, 7 oder 8 Bits/Zeichen

- \* 1, 1 1/2 oder 2 Stoppbits

- \* ungerade, gerade oder keine Parität

- \* Taktvarianten: x 1, x 16, x 32 oder x 64

- \* Erzeugung und Erkennen von Unterbrechungen (Break)

- \* Erkennung von Paritäts-, Überlauf- oder Rahmenfehlern

- byteorientierter Synchronbetrieb

- \* interne oder externe Zeichensynchronisierung

- \* 1 oder 2 SYNC-Zeichen in separaten Registern

- \* 6- oder 8bit-SYNC-Zeichen

- \* automatisches Einfügen und Löschen von SYNC-Zeiche-

- \* Cyclic Redundancy Check (CRC)-Generierung und -Test

- SOLC/HOLC-Betrieb

- \* Generierung und Testen von Abbruchfolge (Abort)

- \* automatische Nulleinfügung und -löschung

- \* automatisches Einfügen von SDLC-Flags in Sendeseguenzen

- \* AdreBfelderkennung

- \* I-Feld-Residuen-Behandlung

- \* CRC-Generierung und -Test

- \* SDLC-Loop-Mode mit EDP-Erkennung; Schleifenan- und -abkopplung

- NRZ-, NRZI oder FM-Kodlerung/-Dekodlerung

- Baud-Rate-Generator (BRG) in jedem Kanal

- Bigital Phase Locked Loop (OPLL) für die Taktgewinnung

- Quarzoszillator

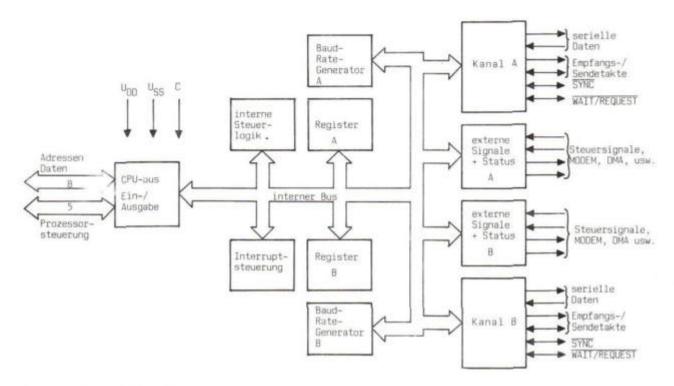

Bild 6: Blockschaltbild

Bild 6 zeigt das Blockschaltbild des SCC. Der empfangene serielle Datenstrom folgt, abhängig vom Zustand der Steuerlogik, einem der verschiedenen Datenwege. Die gesendeten Daten gehorchen einem ähnlichen Steuerungsablauf. Der Datenübertragungsprozeß wird durch die Registerinhalte und die Signale an den Steuerpins bestimmt. Andererseits werden die Register und der Zustand an externen Steuerpins von der internen Logik beeinflusst.

De: U 8030 DC ist auf Systemanwendungen mit Multiplex-AdreG-/Datenleitungen entsprechend denen der "U U 8000 ausgerichtet.

Der U 82530 DC wurde für Systeme entworfen, die separate Adreß- und Datenleitungen haben. Er kommuniziert mit einem Prozessor durch Chip-Select-Eingänge ( $\overline{CS}$  0 und  $\overline{CS}$  1), Read- und Write-Eingänge ( $\overline{RD}$ ,  $\overline{WR}$ ), einen Channel-Select-Eingang ( $\overline{A}/\overline{B}$ ) und einen Data/Control-Eingang ( $\overline{D}/\overline{C}$ ).

#### SCC-Anschlüsse

Die SCC-Pins sind in 7 funktionelle Gruppen unterteilt: Adressen/Daten, Zeitsteuerung und RESET, Systemsteuerung, Interrupt, serielle Daten (beide Kanäle), periphere Steuerung (beide Kanäle) und Takte (beide Kanäle).

Die AdreG-/Datengruppe besteht aus bidirektionalen Leitungen, die benutzt werden, um Daten zwischen der CPU und dem SCC zu übertragen. (Die Adressen werden im U 8030 DC mit A5 bewertet.) Nach Ansprache des SCC durch die CPU hängt die Übertragungsrichtung dieser Leitungen davon ab, ob eine Lese- oder Schreiboperation ausgeführt wird.

Die Zeit- und Steuergruppen kennzeichnen den Typ des ablaufenden Zyklusses. Die Interruptgruppe bearbeitet Ein- und Ausgangssignale, die den Besonderheiten für die Behandlung und Priorisierung von Interrupts im System angepaßt sind. Die übrigen Gruppen können in Kanal-A- und Kanal-B-Datengruppe für serielle Daten (Senden und Empfangen), periphere Steuerung (DMA oder MODEM) und die Eingangs- und Ausgangsleitungen für die Empfangs- und Sendetakte unterteilt werden.

Dieses Datenblatt gibt keine Auskunft über Liefermöglichkeiten und beinhaltet keine Verbindlichkeiten zur Produktion. Die gültige Vertragsunterlage beim Bezug der Bauelemente ist der Typstandard. Rechtsverbindlich ist jeweils die Auftragsbestätigung.

Änderungen im Zuge der technischen Weiterentwicklung vorbehalten.

Die Behandlungsvorschriften für MOS-Bauelemente sind unbedingt einzuhalten, da andernfalls eine Reklamation nicht anerkannt werden kann.

12/87

veb mikroelektronik karl marx erfurt stammbetrieb

DDR-5023 Erfurt, Rudolfstraße 47 Telefon 5 80, Telex 061 306

### elektronik export-import

Volkseigener Außenhandelsbetrieb der Deutschen Demokratischen Republik DDR - 1026 Berlin, Alexanderplatz 6 Telex: BLN 114721 elei, Telefon: 2180