# Information

U82530 DC, U8030 DC

2/88 (13)

Hersteller: VEB Mikroelektronik "Karl Marx" Erfurt

## Serielle Ein-/Ausgabesteuerung

Die Serial Communication Controller (serielle Ein-/Ausgabesteuerung) U 82530 DC und U 8030 DC sindprogrammierbare periphere Schaltkreise in n-Kanal-Silicon-Gate-Technologie. Es sind programmierbare periphere Schaltkreise, die eine umfassende Unterstützung für die Bearbeitung einer Vielzahl serieller Kommunikationsprotokolle gewährleisten.

Bild 1: Anschlußbelegung U 82530 DC

Bild 2: Anschlußbelegung U 8030 DC

Bild 4: Schaltzeichen U 8030 DC

### Bezeichnung und Beschreibung der Anschlüsse

Der SCC ist für Multiplex- (Version U 8030 DC) und Nichtmultiplexbetrieb (Version U 82530 DC) verfügbar. Dementsprechend ist die folgende Anschlußbeschreibung unterteilt in U 8030 DC-spezifische Anschlüsse, U 82530 DC-spezifische Anschlüsse und Anschlüsse, die für beide Versionen identisch sind. Bild 1 (Bild 3) bezeichnet die Anschlüsse und Signalnamen für den U 82530 DC, Bild 2 (Bild 4) die für den U 8030 DC.

#### Anschlußbeschreibung (nur U 82530 DC)

Auswahl Kanal A/Kanal B (Eingang, Kanal A highaktiv) A/B

Dieses Signal wählt den Kanal aus, in den der Schreib- oder Lesezyklus ausgeführt

wird.

CE Chip Enable (Eingang, lowaktiv)

Signal zur Chipfreigabe

DB 0...DB 7 Datenleitungen (bidirektional, tristate)

Anschlußleitungen an den Systemdatenbus

D/C Data/Control (Eingang, Data highaktiv)

Auswahlsignal: Daten oder Steuerinformation

RD Read (Eingang, lowaktiv)

> Während RD = Low ist, liest die CPU aus dem CIO. Während des Interruptbestätigungszyklusses wird mit RD von der CPU der Interruptvektor gelesen.

WR Write (Eingang, lowaktiv)

Dieses Signal zeigt einen Schreibzyklus an. Das gleichzeitige Aktivieren von RD und

WR wird als Hardware-RESET interpretiert.

#### Anschlußbeschreibung (nur U 8030 DC)

AD 0...AD 7 Adre8-/Datenbus (bidirektional, tristate) Multiplexleitungen zum Anschluß an den Adreß-/Datenbus des Systems AS Adress Strobe (Eingang, lowaktiv)

Die Adressen auf AD D...AD 7 werden mit der steigenden Flanke dieses Signals bewertet.

. CS 0 Chip Select O (Eingang, lowaktiv)

Dieses Signal wird gleichzeitig mit den Adressen AD 0... AD 7 bewertet und muß

aktiv sein, damit der entsprechende Zyklus ablaufen kann. CS 0 wird mit AS übernommen.

CS 1 Chip Select 1 (Eingang, highaktiv)

Dieses zweite Auswahlsignal muß ebenfalls aktiv sein, bevor der beabsichtigte Datentransfer über den Systembus ablaufen kann. CS 1 muß während des Transfers aktiv

bleiben.

DS Data Strobe (Eingang, lowaktiv)

Dieses Signal bestimmt den Zeitpunkt für den Datentransfer über den Systembus.

Sind AS und US gleichzeitig Low, so wird dies als Hardware-RESET interpretiert.

R/W Read/Write (Eingang, Read highaktiv)

Dieses Signal kennzeichnet den ablaufenden Zyklus als Lese- oder Schreibzyklus.

#### Anschlußbeschreibung (beide Versionen)

CTSA, CTSB

Clear To Send (Eingänge, lowaktiv)

Wenn diese Anschlüsse "Auto Enable" programmiert sind, gibt ein Low an diesen Eingängen den entsprechenden Sender frei. Wenn sie nicht als "Auto Enable" programmiert sind, können sie wahlfrei genutzt werden. Beide Eingänge sind mit Schmitt-Triggern ausgerüstet, um Signale mit einer längeren Anstiegszeit zu verarbeiten. Der SCC erkennt beliebige Pegelwechsel an diesen Eingängen und kann daraufhin einen Interrupt anfordern.

DCDA, DCDB

Data Cerrier Detect (Eingänge, lowaktiv)

Diese Anschlüsse sind, wenn sie "Auto Enable" programmiert sind, als Empfängerfreigabe vorgesehen. Andernfalls können sie wahlfrei genutzt werden. Beide Eingänge sind mit Schmitt-Triggern ausgestattet, um Signale mit einer längeren Anstiegszeit zu verarbeiten. Der SCC erkennt beliebige Pegelwechsel an diesen Eingängen und kann daraufhin einen Interrupt anfordern.

DTR/REQA, Data Terminal Ready/Request (Ausgänge, lowaktiv)

DTR/REQB Diese Ausgänge folgen dem Zustand des DTR-Bits. Sie können auch wahlfrei oder als Anforderungsleitungen für die DMA-Steuerung genutzt werden.

IEI Interrupt Enable In (Eingang, highaktiv)

Gibt es mehr als einen interruptgesteuerten Schaltkreis im System, wird IEI in Verbindung mit IEO benutzt, um eine Interrupt-Prioritätskette zu realisieren.

Ein High an IEI zeigt an, daß momentan für keinen höherpriorisierten Schaltkreis in der Kette ein Interrupt bedient (Interrupt Under Service) oder angefordert wird.

IEO Interrupt Enable Out (Ausgang, highaktiv)

IEO ist nur dann high, wenn IEI high ist und die CPU keinen SCC-Interrupt bedient

bzw. der SCC keinen Interrupt anfordert. IEO ist mit dem IEI-Eingang des Schaltkreises mit der nächstniedrigeren Priorität verbunden und kann so die Interrupts der

niederpriorisierten Bausteine sperren.

INTACK

Interrupt Acknowledge (Eingang, lowaktiv)

Dieses Signal zeigt einen Interruptanerkennungszyklus an. Während dieses Zyklusses wird die Interrupt-Prioritätskette durchgeschaltet. Wenn DS (U 8030 DC) bzw. RD (U 82530 DC) aktiv werden, sendet der SCC einen Interruptvektor auf den Datenbus (falls IEI high ist). INTACK wird mit der steigenden Flanke von AS bzw. dem Systemtakt bewertet.

INT

Interrupt Request (open-drain-Ausgang, lowaktiv)

Dieses Signal wird aktiviert, wenn der SCC einen Interrupt anfordert.

C

Systemtakt (Eingang)

Dies ist der Grundtakt, der benutzt wird, um die internen Signale zu synchronisieren. Der Takt am SCC braucht keine feste Phasenbeziehung zum Takt des Prozessorsystems zu haben. Die Frequenz des SCC-Taktes muß jedoch mindestens 90 % der Frequenz des Prozessorsystemtaktes betragen. Der Systemtakt wird mit TTL-Pegel getrieben.

RTSA, RTSB

Request To Send (Ausgänge, lowaktiv)

Wenn das RTS-Bit in Schreibregister WR 5 gesetzt ist, wird der RTS-Anschluß Low. Ist das RTS-Bit im Asynchronbetrieb rückgesetzt und wird Auto Enable eingeschaltet, dann geht das Signal, nachdem alle Sendespeicher leer sind, auf High-Pegel. Ist im Synchronbetrieb oder im Asynchronbetrieb Auto Enable ausgeschaltet, so folgt der RTS-Anschluß strikt dem Zustand des RTS-Bits. Beide Anschlüßse können wahlfrei genutzt werden.

RTXCA, RTXCB

Empfangs-/Sendetakt (Eingänge, lowaktiv)

Die Funktionen dieser Anschlüsse müssen durch den Anwender bestimmt werden. In jedem Kanal kann der RTxC-Anschluß den Empfangstakt, den Sendetakt, den Takt für den Baud-Rate-Generator oder den Takt für die DPLL liefern. Der Empfangstakt kann im Asynchronbetrieb das 1-, 16-, 32- oder 64fache der Datenrate betragen. Diese Eingänge können in Verbindung mit den entsprechenden SYNC-Anschlüssen auch für den Aufbau eines Quarzoszillators genutzt werden.

RXDA, RXDB

Empfangsdatenleitungen (Eingänge, highaktiv) Diese Empfangssignale empfangen serielle Daten mit Standard-TTL-Pegel.

SYNCA, SYNCB

Synchronisierung (Ein-/Ausgänge, lowaktiv)

Diese Anschlüsse können entweder als Eingänge, Ausgänge oder als Teil einer Quarzoszillatorschaltung wirken. Im asynchronen Empfangsbetrieb (ohne Quarzoszillator) können diese Anschlüsse wie die CTS- und DCD-Anschlüsse eingesetzt werden. In dieser Betriebsart beeinflussen Pegelwechsel an diesen Leitungen den Zustand des "Sync/Hunt"-Bits im Leseregister RR O, sie haben dann keine andere Funktion.

Im externen Synchronbetrieb (ohne Quarzoszillator) arbeiten diese Leitungen als Eingänge. In dieser Betriebsart muß SYNC, nachdem das letzte Bit des SYNC-Zeichens empfangen worden ist, über zwei Empfangstaktzyklen aktiviert werden. Die Zeichen-

übertragung beginnt mit der steigenden Flanke des Empfangstaktes direkt nach der Aktivierung des SYNC-Anschlusses.

Im Internen Synchrönbetrieb (Monosync und Bisync ohne Quarzoszillator) arbeiten die SYNC-Anschlüsse als Ausgänge und sind nur während des Teils des Empfangszyklusses aktIV, in dem SYNC-Zeichen erkannt werden. Die Synchronbedingung wird nicht gespeichert. So sind diese Ausgänge unabhängig von den Zeichenkettengrenzen, immer wenn ein SYNC-Zeichen erkannt wird, aktiv. Im SOLC-Betrieb arbeiten diese Anschlüsse als Ausgänge und werden beim Empfang eines SDLC-Flags aktiv.

TRXCA, TRXCB

Sende-/Empfangstakte (Eingänge oder Ausgänge, lowaktiv)

Die TRxC-Anschlüsse können als Empfangs- bzw. Sendetakteingänge benutzt werden oder

die Ausgangssignale der DPLL, des Quarzoszillators, des Baud-Rate-Generators oder des

Sendetaktes sein.

TxDA, TxDB

Spendedatenleitungen (Ausgänge, highaktiv) Diese Ausgänge senden serielle Daten mit TTL-Pegel.

W/REQA; W/REQB Wait/Request (Ausgänge, lowaktiv, Wait: open-drain, Request: tristate)

Diese Ausgänge können entweder als Anforderungsleitungen für eine DMA-Steuerung

oder als Wait-Leitungen zur Synchronisation des Datentransfers auf den Systembus

genutzt werden. Der Zustand des Anschlusses nach RESET entspricht Wait.

Bild 5: Gehäuseabmessungen

#### Beschreibung

Die Serial Communication Controller (SCC) U 8030 DC und U 82530 DC sind in n-Kanal-Silizium-Gate-Technologie gefertigt. Es sind programmierbare periphere Schaltkreise, die eine umfassende Unterstützung für die Bearbeitung einer Vielzahl serieller Kommunikationsprotokolle gewährleisten. Der SCC kann für spezielle serielle Kommunikationsverfahren eingesetzt werden, aber auch Standortformate wie byteorientierte synchrone, bitorientierte synchrone und asynchrone Formate bearbeiten. Der Nutzer kann den SCC so programmieren, daß dieser alle asynchronen Formate ohne Einschränkung in bezug auf die Anzahl der Datenbits, die Anzahl der Stopbits oder die Form der Paritätsforderung verarbeitet. In allen Betriebsarten ermöglicht der SCC auch Variationen des Übertragungsprotokolls durch Paritätstest, das Einfügen oder Löschen von Zeichen, CRC-Generierung und Testung, des Erzeugen und Feststellen von Unterbrechung und Abbruch usw.

Der U 82530 DC kann in Systemen mit getrenntem Adreß- und Datenbus wie z.B. U 880-Systemen arbeiten. Der U 8030 DC wird aufgrund seines gemultiplexten Adreß-/Datenbusses vorwiegend in U 8000-Systemen o. a. mit gemultiplextem Bus arbeitenden Prozessorsystemen eingesetzt.

#### Eigenschaften

- Versorgungsspannung: 5 V + 5 %

- max. Taktfrequenz: 4 MHz (6 MHz in Vorbereitung)

- vier unabhängige serielle Ports: zwei Sender- und zwei Empfängerports

- Die maximal mögliche Datenübertragungsrate bei 4 MHz Systemtakt beträgt:

- . Ill bit/s bei NRZ ohne BPLL

- . 250 kbit/s bei FM-Kodierung unter Benutzung der DPLL

- . 125 kbit/s bei NRZI-Kodierung unter Benutzung der DPLL

- alle internen Steuer- und Datenregister sind les- und schreibbar.

- Datonregister sind generell direkt adressierbar, Steuerregister nur beim U 8030 DC

- beim U 82530 DC muB auf die Steuerregister mit einer Befehlsfolge zugegriffen werden

- Vektorinterrupt inklusive Status (Ursache), daisy-chain (IEI, IEO) und Polling möglich

- Der WAIT/REQUEST-Ausgang ermöglicht schnelle CPU/DMA-Blockübertragungen, die DTR/REQUEST-Lei+ung ermöglicht Übertragungen unter DMA-Steuerung in beiden Richtungen (vollduplex)

#### - Asynchronbetrieb:

- . 5, 6, 7 oder 8 Bits/Zeichen

- . 1, 1 1/2 oder 2 Stopbits

- . ungerade, gerade oder keine Parität

- . Taktvarianten: x 1, x 16, x 32 oder x 64

- . Erzeugung und Erkennen von Unterbrechungen (Breaks) ()

- . Erkennung von Paritäts-, Überlauf- oder Rahmenfehlern

#### - byteorientierter Synchronbetrieb

- . interne oder externe Zeichensynchronisierung

- . 1 oder 2 SYNC-Zeichen in separaten Registern

- . 6- oder 8bit-SYNC-Zeichen

- . automatisches Einfügen und Löschen von SYNC-Zeichen

- . Cyclic Redundancy Check (CRC)-Generierung und -Test

#### - SDLC/HDLC-Betrieb

- . Generierung und Testen von Abbruchfolgen (Abort)

- . automatische Nulleinfügung und -löschung

- . automatisches Einfügen von SDLC-Flags in Sendesequenzen

- . AdreGfelderkennung

- . I-Feld-Residuen-Behandlung

- . CRC-Generierung und -Test

- . SDLC-Loop-Mode mit EOP-Erkennung; Schleifenan- und abkopplung

- NRZ-, NRZI oder FM-Kodierung/-Dekodierung

- Baud-Rate-Generator (BRG) in jedem Kanal

- Digital Phase Locked Loop (DPLL) für die Taktgewinnung

- Quarzoszillator

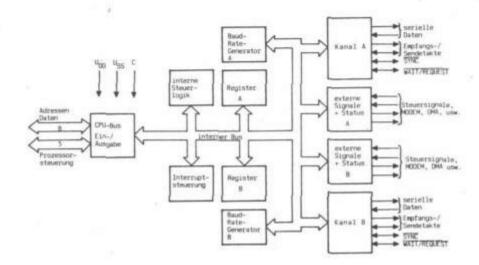

Bild 6: Blockschaltbild

Bild 6 zeigt das Blockschaltbild des SCC. Der Datenübertragungsprozeß wird durch Registerinhalte und Signale an den Steueranschlüssen (Modems) bestimmt.

# $\underline{Grenzwerte}$ (Bezugspotential $U_{SS} = 0 V$ )

|                                 | Kurzzeichen | min. | max. | Einheit        |

|---------------------------------|-------------|------|------|----------------|

| Betriebsspannung                | UCC         | -0,5 | 7    | V              |

| Eingangsspannung                | UI          | -0,5 | 7    | V              |

| Lagerungstempe-<br>raturbereich | stg         | -55  | 125  | o <sub>C</sub> |

Statische und dynamische Kennwerte ( $\phi_a^a = 0...70$  °C;  $U_{CC} = 5 \text{ V} \pm 0,25 \text{ V}; U_{SS} = 0 \text{V}$ )

|                           | Kurzzeichen     | min.                 | mex.                 | Einheit |

|---------------------------|-----------------|----------------------|----------------------|---------|

| Eingangs-<br>spannung Low |                 | -0,5                 | 0,8                  | v       |

|                           | UIL             | -0,5                 | 0,0                  |         |

| Eingangsspannung<br>High  | uIH             | 2                    | U <sub>CC</sub> +0,3 | V       |

| fakteingangs-<br>∍pannung | UICL            | -0,5                 | 0,45                 | ٧       |

|                           | UICH            | U <sub>CC</sub> -0,4 | U <sub>CC</sub> +0,3 | V       |

| usgangsspannung<br>ow     | U <sub>OL</sub> |                      | 0,4                  | v       |

| $I_D = 2 mA$              | 571             |                      |                      |         |

| lusgangsspannung<br>ligh  | U <sub>OH</sub> | 2,4                  |                      | v       |

| $I_0 = -0.25 \text{ mA}$  |                 |                      |                      |         |

| Stromaufnahme             | Icc             | -                    | 200                  | mA      |

| ingangsreststrom          | IIL             |                      | 20                   | μA      |

|                           | IOL             | -                    | 20                   | μA      |

| Taktfrequenz              | f               | 0,25                 | 41)                  | MHZ     |

<sup>1) 6</sup> MHz in Vorbereitung

Ausführliche Unterlagen enthält die "Technische Beschreibung SCC U 82530 DC, U 8030 DC" des VEB Mikroelektronik "Karl Marx" Erfurt - Stammbetrieb.

Diese Datenblatt gibt keine Auskunft über Liefermöglichkeiten und beinhaltet keine Verbindlichkeiten zur Produktion. Die gültige Vertragsunterlage beim Bezug der Bauelemente ist der Typstandard. Rechtsverbindlich ist jeweils die Auftragsbestätigung.

Änderungen im Zuge der technischen Weiterentwicklung vorbehalten.

Die Behandlungsvorschriften für MOS-Bauelemente müssen unbedingt eingehalten werden, da andernfalls eine Reklamation nicht anerkannt werden kann.

Die vorliegenden Datenblätter dienen ausschließlich der Information! Es können daraus keine Liefermöglichkeiten oder Produktionsverbindlichkeiten abgeleitet werden. Änderungen im Sinne des technischen Fortschritts sind vorbehalten.

Herausgeber:

veb applikationszentrum elektronik berlin im veb kombinet mikroelektronik

Mainzer Straße 25

Berlin, 1035

Telefon: 5 80 05 21, Telex: 011 2981 011 3055