## mikreektronik

Pan

# Information

## Graphic - Display - Controller U 82720 D

Der U 82720 D (Graphic-Dispiay-Controller/GDC) ist ein Mikrorechneranwendungen angepaßter Controllerschaltkreis zur Steuerung von Rastergrafik- bzw. alphanumerischen Displays. Der GDC wird dabel zwischen Bildwiederholspeicher und Systemprozessor im Display angeordnet. Der GDC übernimmt die Verwaltung des Bildwiederholspeichers und die Erzeugung der Steuersignale für das Videointerface.

| 2×WCLK       | 1  | 40 UCC   |   |

|--------------|----|----------|---|

| DBIN         | 2  | 39 A 17  |   |

| HSYNC        | 3  | 38 A 16  |   |

| WEXT<br>SYNC | 4  | 37 AD 15 | 5 |

| BLANK        | 5  | 36 AD 14 | 4 |

| ALE          | 6  | 35 AD 1  | 3 |

| DRQ          | 7  | 34 AD 12 | 2 |

| DACK         | 1  | 33 AD 1  | 1 |

| RD           | 9  | 32 AD 1  | 0 |

| WR           | 10 | 31 AD 9  | 9 |

| A 0          | 11 | 30 AD (  | 8 |

| DB 0         | 12 | 29 AD 1  | 7 |

| DB 1         | 13 | 28 AD 6  | ô |

| DB 2         | 14 | 27 AD 5  | 5 |

| DB 3         | 15 | 26 AD 4  |   |

| DB 4         | 16 | ZS AD :  | 3 |

| DB 5         | 17 | 24 AD 2  | 2 |

| DB 6         | 18 | 23 AD 1  |   |

| DB 7         | 19 | 22 AD 0  | ) |

| GND          | 20 | 21 LPE   | N |

| 12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | DB 0<br>DB 1<br>DB 2<br>DB 3<br>DB 4<br>DB 5<br>DB 6<br>DB 7 | GDC | AD 0<br>AD 1<br>AD 2<br>AD 3<br>AD 4<br>AD 5<br>AD 6<br>AD 7 | 22<br>23<br>24<br>25<br>26<br>27<br>28<br>29 |

|----------------------------------------------|--------------------------------------------------------------|-----|--------------------------------------------------------------|----------------------------------------------|

| 9<br>10<br>11                                | RD<br>WR<br>A 0                                              |     | AD 8<br>AD 9<br>AD 10<br>AD 11<br>AD 12                      | 30<br>31<br>32<br>33<br>34                   |

|                                              |                                                              |     | AD 13<br>AD 14<br>AD 15                                      | 35<br>36<br>37                               |

|                                              |                                                              |     | A 16<br>A 17                                                 | 38<br>39                                     |

|                                              |                                                              |     | ALE<br>DBIN                                                  | <u>6</u><br>2                                |

| 21                                           | 2 X<br>WCLK<br>LPEN                                          |     | HSYNC<br>V/EXT<br>SYNC<br>BLANK                              | 3<br>4<br>5                                  |

| 8                                            | DACK                                                         |     | DRG                                                          | 7                                            |

Bild 1: Anschlußbelegung und Schaltungskurzzeichen

Bay 5

Bezeichnung der Anschlüsse: 2 × WCLK TakteIngang Buseingangssignal als Strobesignal zum Einlesen der Daten des Bild-DBIN wiederholspeichers **HSYNC** Ausgang Horizontalsynchronisationssignal zur Erzeugung des Zellenrücklaufs auf dem Display Eln-/Ausgang Vertikalsynchronisationssignal zur Erzeugung des Bildrücklaufs auf dem Display (Ausgangssignal); in der GDC-Slave-Betriebsart als Eingangssignal V/EXT SYNC zur Synchronisation des Bildrasterzeitverhaltens mit einem Master-GDC BLANK Ausgang Videoaustastsignal Ausgang Speicherzyklussignal für Zeilenübernahme (RAS-Signal) für dynamische RAMs oder Demultiplexsignal (ALE-Signal = Adress Latch Enable) für den Adreß-/ ALE Ausgang DMA-Anforderungssignal (DMA-Request) zur Steuerung eines externen DMA-DRO DACK Eingang DMA-Bestätigungssignal (DMA-Acknowledge) zur Steuerung eines externen DMA-Controllers RD Eingang Strobesignal (Read) zum Einlesen von GDC-Daten in den System-Mikro-WR Eingang Strobesignal (Write) zum Einlesen von Mikrprozessordaten in den GDC Eingang Auswahl der Adresse zur Unterscheidung von Kommandos und Lese-/ A O Schreibdaten Ein-/Ausgänge bidirektionaler Mikroprozessor-Datenbus des GDC, Bussteuerung erfolgt mit den Signalen  $\overline{WR}$  für Eingabe und  $\overline{RD}$  für Ausgabe DB 0 ... DB 7 GND Bezugspotential 1 PEN Eingang Lichtstiftsignal (Lihgt Pen Detect) AD 0 ... AD 12 Ein-/Ausgänge; Adre6-/Datenbus des Bildwiederholspeichers (Bit 0 ... 12) Ein-/Ausgänge; Funktion wird entsprechend der Betriebsart des GDC festgelegt:

- bei Grafik-Betriebsart: Adres-/Datenbus des Bildwiederholspeichers AD 13 ... AD 15 (Bit 13 ... 15) Zeilenzählerausgänge (Bit 13 ... 15) - bei Zeichen-Betriebsart: Adreß-/Datenbus des Bildwiederholspeichers (Bit 13 ... 15) - bei Misch-Betriebsart: A 16 Ausgang; Funktion wird entsprechend der Betriebsart des GDC festgelegt: - bei Grafik-Betriebsart: - bei Zeichen-Betriebsart: Adresbus des Bildwiederholspeichers (Bit 16) Zeilenzählerausgang (Bit 3) - bei Misch-Betriebsart: Attributblinksignal und Rücksetzen

Zeilenzählers

Ausgang; Funktion wird entsprechend der Betriebsart des GDC festgelegt:

- bei Grafik-Betriebsart: Adreßbus des Bildwiederholspeichers (Bit 17) A 17 - bei Grafik-Betriebsart: - bei Zeichen-Betriebsart: Cursor- und Zellenzählerausgang (Bit 4) Cursorausgang und Flaganzeige - bel Misch-Betriebsart: Bildbetrlebsart

ucc Betriebsspannung +5 V

Bild 2: Gehäuseabmessungen

#### Kurzbeschreibung

- Der GDC ist schaltungskonzeptionell zwischen dem Bildwiederholspeicher und dem Mikroprozessor

- Folgende wesentliche Eigenschaften charakterisieren den GDC:

- . geeignet für hochauflösende Bildschirme, max. 1024 x 1024 Punkte

- , Der Bildwiederholspeicher kann in beliebiger Größe bis zu 4 Mbit (256 kWorte x 16 bit) aufgebaut werden.

- . Ansteuerung von monochromen S/W- und Farbdisplays möglich

- . Betriebsarten: 1. Grafik-Mode

- - 2. alphanumerischer Mode

- 3. Misced Mode

- . In allen Betriebsarten ist zooming, panning und windowing möglich.

- . Darstellung alphanumerischer Zeichen, Punkte, Linien, Rechtecke und Kreisbögen möglich

- , Lichtstifteingang

- . 4 MHz Taktfrequenz

- , eine Versorgungsspannung von +5 V

#### Beschreibung

Der U 82720 D - Graphic Display Controller (GDC) ist ein Mikrorechneranwendungen angepaßter Controllerschaltkreis zur Steuerung von Rastergrafik- bzw. alphanumerischen Displays. Der GDC wird dabel zwischen Bildwiederholspeicher (Display Memory) und Systemmikroprozessor im Display angeordnet. Der GDC übernimmt die Verwaltung des Bildwiederholspeichers und die Erzeugung der Steuersignale für das Video-Interface.

Der GDC U 82720 Dermöglicht, insbesondere bei Systemen mit mehreren GDCs im Master-Slave-Betrieb, den Aufbau hochauflösender grafischer Displays mit dem Prinzip der Bilddarstellung nach dem Rasterdarstellungsverfahren.

Beim Rasterdarstellungsverfahren wird der Elektronenstrahl einer Katodenstrahlröhre horizontaler und vertikaler Richtung zeilenförmig periodisch abgelenkt, d. h. Zeile für Zelle über den Bildschirm geführt und jeweils dort angeschaltet (hellgetastet), wo ein heller Punkt entstehen soil. Striche, Buchstaben und grafische Zeichen werden immer aus zusammengesetzt.

Der Aufwand für die Erarbeitung der Steuersoftware für ein grafisches Displays kann durch den komfortablen Befehlssatz des GDC und die verfügbaren Zeichnungsalgorithmen zum Zeichnen grafischer Darstellungen klein gehalten werden.

Der vom GDC verwaltete Bildwiederholspeicher kann in den verschiedensten Formaten und Größen bis hin zu 256 kWorten zu je 16 bit konfiguriert werden. Die Darstellungen auf dem Bildschirm können vergrößert (zooming) werden. Das Bewegen bzw. Schwenken einer Darstellung (panning) kann softwaregesteuert ablaufen. Es können gleichzeitig mehrere Teile des Bildwiederholspeichers als sog. Ausschnitte (Fenster) auf dem Bildschirm dargesteilt werden (windowing).

Der Lichtstifteingang eignet sich besonders zur Interaktiven Benutzerkommunikation am Grafik-Display.

#### Spezifikationen des GDC U 82720 D

- Mikroprozessor-Interface; DMA-Transfer in Verbindung mit DMA Controllern möglich

- Kommandospeicherung in GDC-Internem FIFO-Buffer

- Bildwlederholspeicher, adressierbar 256 kWorte zu je 16 bit; Zugriffsmöglichkeit über Read-Modify-Write-Zykius (RMW) und Display-Zykius ohne RMW

- Eingang für Lichtstift

- Möglichkeit der externen Videosynchronisation

- Grafik-Betriebsart (Graphic Mode) programmierbar; Verwaltung von 4 Mbit Bildwiederholspeicher Möglichkeiten der Grafikdarstellung:

Zeichnen von Geraden, Kreisbögen, Rechtecken und grafischen Zeichen mit einer Punktfolgefrequenz von 32 MHz in der normalen bzw. 64 MHz in der "gedehnten" Darstellungsart (Wide Display Mode); Bildgröße bis zu 1024 x 1024 Pixel in 4 Bildebenen in Farbe oder Graustufen; 2 unabhängig voneinander "rollbare" Bildfenster

- Zeichen-Betriebsart (Character Mode) programmierbar; Verwaltung eines Bildwiederholspeichers mit 8 k x 13bit Charakter- und Attributspeicher

Möglichkeiten der Zeichendarstellung:

automatische Verschiebung des Cursors; 4 unabhängig voneinander rollbare Flächen; programmierbare Cursorgröße; 256 Zeichen pro Zeile; bis zu 100 Zeilen je Bildebene

- gemischte Grafik- und Zeichen-Betriebsart (Mixed Graphic and Character Mode) programmierbar; Verwaltung von 64 kZeichen Bildwiederholspeicher und ein Megapixel Grafik-Bildwiederholspeicher

- Vergrößerungsfaktor (Zoom) 1 ... 16fach; Schwenkfunktion (panning); programmierbare Parameter für das Video-Raster

- DMA-Elgenschaften: Übertragung von Byte oder Wort in vier Taktperioden je Byte-Übertragung

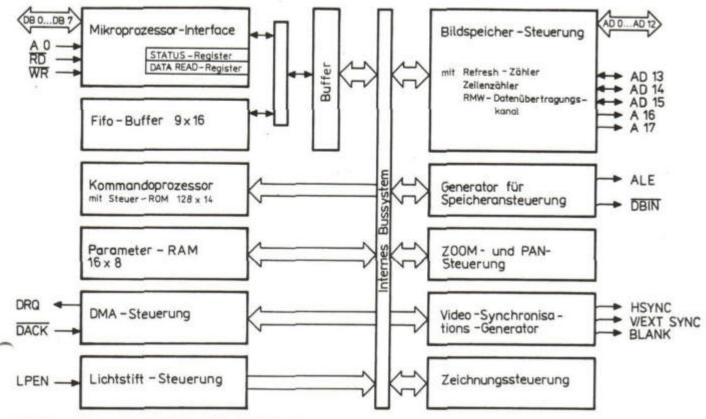

Nachfolgend werden die Elemente des Blockschaltbildes beschrieben:

#### Mikroprozessor-Interface

Das Mikroprozessor-Interface mit den Datenbus-Ein-/Ausgängen DB 0 ... DB 7 ist 8 bit breit und bidirektional ausgeführt. Zum Interface gehören das Statusregister und das Data-Read-Register. Das Statusregister ist zu jedem beliebigen Zeitpunkt lesbar. Ein zusätzlicher FiFO-Buffer hat die Organisation 9 x 16 bit. Der Zugriff zum FiFO-Buffer wird mit den Flags des Statusregisters sowie in Abhängigkeit von den verschiedenen internen GDC-Operationen koordiniert.

Bild 3: Blockschaltbild des GDC U 82720 D

Nachfolgend werden einzelnen Bits eines Registers, die eine besondere Bedeutung haben, einheitlich als Flag und mit ihrem Namen bezeichnet (Beispiel: Image Flag).

#### Kommandoprozessor

Die Inhalte des FIFO-Buffers werden mit dem Kommandoprozessor Interpretiert. Dabei erfolgt eine Dekodierung der im FIFO befindlichen Kommandobytes und die Verteilung der Befehlsparameter an Ihre Bestimmungsorte im GDC. Bei gleichzeitigem Zugriff von Businterface und Kommandoprozessor auf den FIFO-Buffer hat das Businterface die höhere Priorität.

#### DMA-Steuerung

Die DMA-Steuerung des GDC übernimmt die Datenübertragung am Mikroprozessor-Businterface, wenn mit einem externen DMA-Controller kommuniziert wird. Die Steuersignale für DMA-Anforderung DREQ (DMA-Request) sowie DMA-Bestätigung DACK (DMA-Acknowledge) können im Handshake-Betrieb für die Ansteuerung beliebiger DMA-Controller (z. B. UA 858 D) verwendet werden. Damit ist es möglich, die Display-Daten im direkten Speicherzugriff zwischen dem Systemspeicher des steuernden Mikroprozessors und dem Bildwiederholspeicher des GDC zu übertragen.

#### Parameter-RAM

Der 16 Byte tiefe RAM speichert Befehlsparameter, die während des Darstellungs- und Zeichnungsprozesses wiederholt abgefragt werden. In der Zeichen-Betriebsart enthält der RAM die Display-Flächenaufteilungsparameter. In der Grafik-Betriebsart werden die Zeichnungspattern und Grafikelemente gespeichert.

#### Video-Synchronisationsgenerator

Der Generator der Videosynchronisationslogik des GDC erzeugt basierend auf der Taktfrequenz das Rasterzeitverhalten für fast alle Zeilensprung- und Nichtzellensprungformate sowie für das "Wiederholungsfeld" beim Zeilensprungformat.

Die Programmierung des Video-Synchronisationsgenerators erfolgt nach RESET. In der sog. Slave-Betriebsart koordiniert der Generator das Video-Zeitverhalten zwischen dem GDC und einem anderen Videosignalerzeuger.

#### Generator für Speicheransteuerung

Ein Generator zur Erzeugung des Speicherzeitverhaltens ermöglicht die Bereitstellung von zwei Speicherzyklustypen: einem 2-Takt-Display-Zyklus sowie einem Read-Modify-Write-Zyklus (RMW) mit 4 Taktzyklen. Als Signale zur Ansteuerung des Bildwiederholspeichers stehen die Speicherzyklussignale RAS (ALE) und DBIN zur Verfügung. Die beiden Signale erzeugen das Zeitverhalten und die Steuerinformation zur Koordinierung der externen Hardware mit dem GDC-Businterface.

Das Signal ALE (Adress Latch Enable) kennzeichnet den Beginn eines jeden Speicherzyklusses. Mit der Aktivierung des DBIN-Ausganges kennzeichnet der GDC die Zeit Innerhalb eines RMW-Zyklusses, in der die an den RAMs des Bildwiederholspeichers anliegenden Daten akzeptiert werden.

#### Zoom- und Pan-Steuerung

Der GDC ermöglicht unter Einsatz externer Hardware die Anwendung der programmierbaren Vergrößerung der Darstellung auf dem Bildschirm. Gleichfalls ist eine Schwenkbewegung über die für die Bilddarstellung benutzte Display-Bildfläche möglich.

Entsprechend der programmlerten und im Parameter-RAM gespeicherten Information zum Vergrößerungsfaktor und zur Bildfläche des Displays bestimmt die GDC-Interne Zoom- und Pan-Steuerung, wann zur nächsten Speicheradresse für den Bildaufbau bzw. zur nächsten Display-Bildfläche übergegangen wird.

Das Grundprinzip für die Realisierung von Vergrößerungen besteht in der wiederholten hinterbzw. untereinanderfolgenden Abbildung von Punkten mit gleichen Daten.

Durch das wiederholte Abbilden gleicher Bildpunkte in einer Zeile bei unveränderter Punktfolgefrequenz wird dabei eine Bildvergrößerung in horizontaler Richtung erreicht. Die entsprechende Bildvergrößerung in vertikaler Richtung erfolgt durch wiederholte Abbildung von Punkten mit den Daten der vorangegangenen Zeilen. Die Zoom-Fähigkeit ist nur beim bitweisen Grafikbetrieb möglich.

Falls die Zeilenzahl für eine Display-Bildfläche erschöpft ist, entnimmt die Zoom-Steuerung die Startadresse und die Anzahl der Zeilen für die nächste Display-Bildfläche vom Parameter-RAM.

Der System-Mikroprozessor kann durch Veränderung der Startadresse einer Display-Bildfläche das Schwenken in jede Richtung unabhängig von anderen Display-Bildflächen erreichen.

#### Zeichnugssteuerung

Der Zeichnungsprozessor dieser Steuerung enthält die für die Berechnung der Pixeladressen und -positionen von diversen grafischen Darstellungen notwendige Logik. Außer einem gegebenen Startpunkt und entsprechenden Zeichnungsparametern benötigt der Zeichnungsprozessor keine weitere Unterstützung, um die Darstellung vollständig zu zeichnen.

#### Bildwiederholspeichersteuerung

Die Aufgaben der Steuerung des Bildwiederholspeichers sind vielfältig. Am wichtigsten ist das Multiplexen der Adreß- und Dateninformationen vom und zum Bildwiederholspeicher des GDC. Die Steuerung enthält 16bit-Logikeinheiten, um den Inhalt des Bildwiederholspeichers während der RMW-Zyklen ändern zu können. Weiterhin erfolgt die Ansteuerung des Zeilenzählers in der Zeichen-Betriebsart und des Refreshzählers für dynamische RAMs im Bildwiederholspeicher. Gleichfalls bemißt die Steuerung die Video-Rasterzeit in den verschiedenen Zyklusarten.

#### Lichtstiftsteuerung

Für den Fall, daß zwei steigende Flanken am Lichtstifteingang dem selben Punkt zweier aufeinanderfolgender Video-Raster entsprechen, werden die impulse als gültige Lichtstiftinformationen anerkannt. Ein Statusbit des GDC zeigt danach dem System-Mikroprozessor an, daß das Lichtstiftregister eine gültige Adresse enthält.

Die Anwendungsmöglichkeiten für den GDC U 82720 D sind vielfältig, da er die Realisierung folgender Eigenschaften unterstützt:

- hohe Dotfrequenz

- Farbflächen

- horizontal begrenzte Bildschirmwindows

- charakterorientlerter Bildschirm

- gemischtes Grafik- und Charakterdisplay

Internationaler Vergleichstyp

1 82720

Eine ausführliche Beschreibung des U 82720 D liegt als "Technische Beschreibung U 82720 D" im VEB Mikroelektronik "Karl Marx" Erfurt - Stammbetrieb vor. Die Bestellung der technischen Beschreibung ist unter folgender Adresse möglich:

VEB Mikroelektronik "Karl Marx" Erfurt Stammbetrieb Abt. Absatz, Tel. 58 26 98 Rudolfstraße 47 Erfurt 5 0 2 3

Dieses Datenblatt gibt keine Auskunft über Liefermöglichkeiten und beinhaltet keine Verbindlichkeiten zur Produktion. Die gültige Vertragsunterlage beim Bezug der Bauelemente ist der Typstandard. Rechtsverbindlich ist jewells die Auftragsbestätigung.

Änderungen in Zuge der technischen Weiterentwicklung vorbehalten.

Die Behandlungsvorschriften für MOS-Bauelemente sind unbedingt einzuhalten, da andernfalls eine Reklamation nicht anerkannt werden kann.

10/86

## veb mikroelektronik karl marx erfurt stammbetrieb

DDR-5023 Erfurt, Rudolfstraße 47 Telefon 5 80, Telex 061 306

### elektronik export-import

Volkseigener Außenhandelsbetrieb der Deutschen Demokratischen Republik DDR - 1026 Berlin, Alexanderplatz 6 Telex: BLN 114721 elei, Telefon: 2180