# Information

## Floppy - Disk - Controller U 8272 D

Der U 8272 D ist ein Steuerschaltkreis für Folienspeicher (Floppy Disk) zur Organisation des Datenaustausches zwischen der CPU und max. 4 Floppy-Disk-Laufwerken.

| RESET 1            | 40 UCC       |

|--------------------|--------------|

| RD 2               | 39 RW/SEEK   |

| WR 3               | 38 LCT/DIR   |

| CS 4               | 37 FRISTP    |

| A0 5               | 36 HOL       |

| DB 0 6             | 35 RDY       |

| DB 1 7             | 34 WP/TS     |

| DB 2 8             | 33 FLT/TRU 0 |

| DB 3 9             | 32 PS 0      |

| DB 4 10            | 31 PS 1      |

| DB 5 11            | 30 WR DATA   |

| DB 6 12            | 29 DS 0      |

| DB 7 13            | 28 DS 1      |

| DRG 14             | 27 HDSEL     |

| DACK 15            | 26 MFM       |

| TC 16              | 25 WE        |

| 1DX T7             | 24 VCO       |

| INT 18             | 23 RO DATA   |

| CLK 19             | 22 DW        |

| U <sub>SS</sub> 20 | 21 WRCLK     |

| 4                                                                | RESET                                                                                                | DRQ<br>INT                                       | 18                         |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------|

| 2<br>3<br>5<br>15<br>16                                          | ORD<br>OWR<br>A 0<br>ODACK<br>TC<br>CLK                                                              | WR<br>DATA<br>WE<br>PS 1<br>PS 0<br>VC0          | 30<br>25<br>31<br>32<br>24 |

| 21<br>23<br>22                                                   | WRCLK<br>RD<br>DATA<br>DW                                                                            | DS 0<br>DS 1<br>MFM                              | 29<br>28<br>26             |

| 35<br>34<br>17<br>33<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | RDY<br>WP/TS<br>IDX<br>FLT/<br>TRU 0<br>DB 0<br>DB 1<br>DB 2<br>DB 3<br>DB 4<br>DB 5<br>DB 6<br>DB 6 | RW/<br>SEEK<br>HDL<br>HDSEL<br>LCT/DIR<br>FR/STP | 39<br>36<br>27<br>38<br>37 |

Bild 1: Anschlußbelegung und Schaltzeichen

#### Bezeichnung der Anschlüsse:

```

1

RESET

RESET: Erzeugung des Grundzustandes

2

READ: Steuersignal für Datenübertragung

WR

3

WRITE: Steuersignal für Datenübertragung

CS

CHIP SELECT: Schaltkreisanwahl

5

40

AO: Daten- und Statusregisteranwahlsignal

6 - 13 DB D ... DB 7

Datenbus

DMA-REQUEST: DMA-Anforderung

14

DRO

15

DACK

DMA-ACKNOWLEDGE: DMA-Bestätigung

16

TE

TERMINAL COUNT: Beendigung des DMA-Transfers

17

IDX

INDEX: Anzeigen des Beginns einer Diskettenspur

18

INT

INTERRUPT: Interruptanforderung

19

CLK

CLOCK: Einphasen-Rechtecktakt

20

USS

Masse

21

WRCLK

WRITE CLOCK: Datenschreibtakt

22

DW

DATA WINDOW: Datenbegleitsignal vom FDD

23

RD DATA

READ DATA: Daten vom FDD

24

VCO

VCO: Regelung des Oszillators der PLL

WE

25

WRITE ENABLE: Freigabesignal zum Datenschreiben

MEM

26

MFM: Datenschreibmodus

HOSEL

27

HEAD SELECT: Kopfauswahl

28. 29

05 0, 05 1

DRIVE SELECT: Auswahlsignal für die Laufwerke

30

WR DATA

WRITE DATA: Schreibleitung der seriellen Takt- und Datenbits zum FDD

PS 0, PS 1

PRECOMPENSATION: Schreiben des Vorabgleichstatus bei MFM

31, 32

FAULT/TRU 0

33

FAULT/TRACK 0: Fehlermeldung des FDD, Spur 0

WRITE PROTECT/TWOSIDE: Prüfung auf Schreibschutz/zweiseitige Diskette

34

WP/TS

35

RDY

READY: Bereitschaft des FOO

HDL.

HEAD LOAD: Befehl bewirkt Aufsetzen des Lese-/Schreibkopfes auf die Diskette

36

FR/STP

FAULT und RESET/STEP: Rücksetzen des Fehler-FF in FDD/Schrittimpulse

37

für die Kopfposition

LOW CURRENT/DIRECTION: Reduzieren des Kopfschreibstromes/Festlegung

LCT/DIR

38

Konfbewegung

RW/SEEK

39

READ/WRITE/SEEK: Auswahl des Betriebsmodus

40

Betriebsspannung +5 V

```

#### Kurzbeschreibung

- Steuerschaltkreis für Folienspeicher (Floppy Disk) zur Organisation des Datenaustausches zwischen einer CPU und max. 4 Floppy-Disk-Laufwerken

- geeignet für Standard-Floppy (8") U 8272 D 08 und Mini-Floppy (5,25") U 8272 D 04

- programmierbare Aufzeichnungslänge von 128, 256, 512 oder 1024 Byte/Sektor

- Kompatibilität zum IBM-Einfach- (FM, einfache Dichte) und Doppelformat (MFM, doppelte Dichte)

- Mehrfachsektor- und Mehrfachspurübertragungsfähigkeit

- Datentransport wahlweise (programmierbar) im DMA- oder NON-DMA-Modus

- Daten- und Adressensuchfähigkeit

- 15 einsatzsspezifische Befehle

- Erzeugung zahlreicher Steuersignale (für externe PLL, Schreibvorabgleich usw.) und Statusinformation

- Programmierung durch CPU

- geeignet für zahlreiche CPU-Typen, einschließlich U 880 D

- Taktfrequenz: 8 MHz für U 8272 D 08 und 4 MHz für U 8272 D 04

- Betriebsspannung: +5 V

- 40poliges DIL-Plastgehäuse

- nSGT-Herstellungstechnologie

- Typspektrum: U 8272 D 08

#### Funktionsbeschreibung

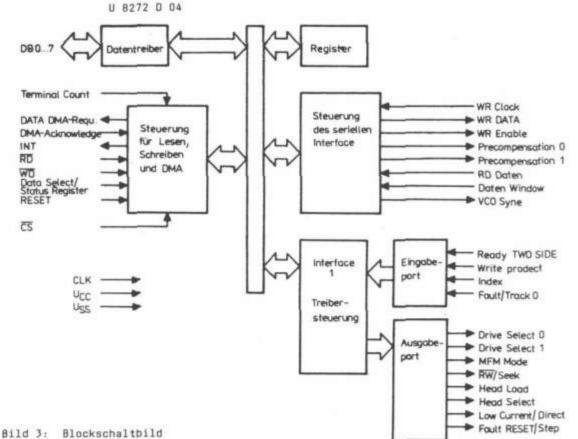

Der Floppy-Disk-Controller (FDC) U 8272 D ist ein Steuerschaltkreis für Floppy-Disk-Laufwerke; er organisiert den Datenaustausch zwischen einem Prozessor (CPU) und bis zu 4 (Standard- oder Mini-) Floppy-Disk-Laufwerken. Hierzu besitzt er 15 einsatzorientierte, nachstehend aufgeführte Befehle (sog. Kommandos):

- Daten lesen

- Lesen ignorierter Daten

- Lesen einer Spur

- Formatieren einer Spur

- Testen kleiner oder gleich

- Rücksetzen

- Abfragen des Interrupt-Status

- Suchen

- Daten schreiben

- Schreiben ignorierter Daten

- Lesen eines Identifikationsfeldes

- Testen auf Datengleichheit

- Testen größer oder gleich

- Wertzuweisung

- Abfragen des Treiberstatus

Im Rahmen der Befehlsabarbeitung werden vom FDC zahlreiche Interface-Steuersignale erzeugt, z.B. Signale für den Aufbau einer externen PLL, Schreibvorabgleichschaltung usw. Nach beendeter Abarbeitungsphase sendet der FDC ein Interruptsignal (INT = 1) und danach müssen alle geforderten Leseoperationen von der CPU ausgeführt werden.

Der U 8272 D enthält zwei Bbit-Register, auf die die CPU über den Datenbus bzw. Systembus jederzeit zugreifen kann. In diesen Registern können Daten (Eingabe- und Ergebnisdaten), die Befehlscodes für die o.g. Befehle (Programmierung), Laufwerkstatusinformationen usw. gespeichert werden. Das Statusregister, der Vereinfachung des Datenaustausches zwischen der CPU und dem FDC dienend, kann von der CPU nur gelesen werden. Zwischen den Kommandos und Schrittimpulsen fragt der FDC seriell die einzelnen Laufwerke hinsichtlich ihres "Bereitsignales" ab; hat sich eines dieser Signale geändert, sendet der FDC ein Interruptsignal aus. Spurschrittrate, Kopflade- und -entladezeit sind vom Anwender programmierbar. Der FDC besitzt eine interne Adreßmarkensuchschaltung sowie Mehrfachsektor- und Mehrfachspurübertragungsfähigkeit.

Mit Hilfe der erzeugten Anforderungssignale ist es möglich, DMA-Operationen mit einem externen Controller (z. 8. U 858 D) selbständig durchzuführen bzw. über eine Unterbrechungsmeldung im NON-DMA-Modus zu arbeiten. Bei DMA-Betrieb braucht die CPU lediglich die entsprechenden Befehle in den FDC zu leden; der gesamte Datenaustausch wird dann von FDC und DMA-Controller gesteuert. Der durch den FDC realisierbare Datenaustausch kann sowohl über das IBM-Einfachformat (FM), Sytem 3740, als auch über das IBM-Doppelformat (MFM), System 34, einschließlich der Doppelseitenbeschreibung erfolgen.

#### Grenzwerte (Alle Spannungen sind auf U<sub>SS</sub> = 0 V bezogen.)

| Kennwert            | Kurzzeichen | min. | max. | Einheit |

|---------------------|-------------|------|------|---------|

| Betriebsspannung    | ucc         | -0,5 | 7,0  | V       |

| Eingangsspannung    | UT          | -0,5 | 7,0  | V       |

| Ausgangsspannung    | l un        | -0,5 | 7,0  | V       |

| Verlustleistung     | Pv          |      | 1,5  | W       |

| Umgebungstemperatur | 9°          | 0    | 70   | *C      |

| Lagertemperatur     | detg        | -55  | 125  | *c      |

#### Betriebsbedingungen (Alle Spannungen auf $U_{SS} = 0 \text{ V bezogen.}$ )

| Kennwert                                                        | Kurzzeichen                               | min. | max.      | Einheit |

|-----------------------------------------------------------------|-------------------------------------------|------|-----------|---------|

| Betriebsspannung                                                | ucc                                       | 4,75 | 5,25      | V       |

| Eingangsspannung L                                              | U <sub>IL</sub> 1)                        | -0,5 | 0,8       | v       |

| ingangsspannung H                                               | U <sub>TH</sub> 1)                        | 2,0  | UCC + 0,5 | V       |

| imgebungstemperatur                                             | 9,                                        | 0    | 70        | *c      |

| aktperiode                                                      | U <sub>IH</sub> 1)  Sa t <sub>CY</sub> 2) | 125  | 500       | пв      |

| mpulszeiten                                                     | t <sub>AR</sub>                           | . 0  |           | ns      |

| t <sub>AW</sub> t <sub>WA</sub> t <sub>WW</sub> t <sub>DW</sub> |                                           | 250  |           | ns      |

|                                                                 |                                           | 0    |           | ns      |

|                                                                 |                                           | 0    |           | ns      |

|                                                                 |                                           | 250  |           | ns      |

|                                                                 | Of Carren                                 | 150  |           | ns      |

|                                                                 | two                                       | 5    |           | ns      |

|                                                                 | t <sub>ROD</sub> 3)                       | 40   |           | ns      |

|                                                                 | t <sub>ROW</sub> 3)                       | 15   |           | ns      |

| t <sub>WRD</sub> 3)                                             | t <sub>WRO</sub> 3)                       | 15   |           | ns      |

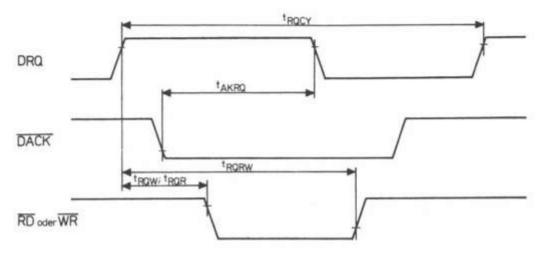

|                                                                 | t <sub>RQRW</sub> 3)                      |      | 12        | μs      |

|                                                                 | t <sub>RQR</sub> 3)                       | 800  |           | ns      |

|                                                                 | t <sub>RQW</sub> 3)                       | 250  |           | ns      |

| ykluszeit MFM = O                                               | t <sub>WWCY</sub> 3)                      | 2    |           | μs      |

| MFM = 1                                                         | and t                                     | 1    |           | μs      |

#### Statische Kennwerte (Alle Spannungen auf $U_{SS} = 0 \text{ V bezogen.}$ )

| Kennwert           | Kurzzeichen     | Meßbedingungen                                        | min. | max. | Einheit |

|--------------------|-----------------|-------------------------------------------------------|------|------|---------|

| Ausgangsspannung L | UDL             | U <sub>CC</sub> = 4,75 V; I <sub>OL</sub> = 2,0 mA    |      | 0,45 | V       |

| Ausgangsspannung H | U <sub>OH</sub> | U <sub>CC</sub> = 4,75 V;  I <sub>OH</sub>   = 200 μA | 2,4  |      | V       |

| Stromaufnahme      | ICC             | 10000                                                 | 1    | 250  | mA      |

| Kennwert     | Kurzzeichen        | min. | max.                    | Einheit |

|--------------|--------------------|------|-------------------------|---------|

| Impulszeiten | t <sub>RD</sub>    |      | 200                     | ns      |

|              | t <sub>DF</sub>    | 20   | 100                     | ns      |

|              | t <sub>RI</sub> 3) |      | 500                     | ns      |

|              | t <sub>WI</sub> 3) |      | 500                     | ns      |

|              | tRQCY              | 104  |                         | ns      |

|              | tAKRQ              |      | 200                     | ns      |

|              | t <sub>FR</sub>    | 64   | 80                      | ns      |

|              | tus                | 96   |                         | ns      |

|              | t <sub>SD</sub>    | 56   |                         | ns      |

|              | t <sub>DST</sub>   | 8    |                         | ns      |

|              | t <sub>STU</sub>   | 40   |                         | ns      |

|              | t <sub>STD</sub>   | 192  |                         | ns      |

|              | t <sub>STP</sub>   |      | 40 . t <sub>CY</sub> 4) | ns      |

|              | t <sub>SC</sub> 3) | 264  |                         | ns      |

#### Bedingungen

- 1) gilt nicht für CLK und WRCLK

- 2) für Typ U 8272 D 04 beträgt der Kleinstwert für  $t_{CY}$  = 250 ns 3) Werte gelten für Standard-Floppy (8 MHz-Takt), bei Mini-Floppy (4 MHz-Takt) sind die Werte zu verdoppeln

- 4) typisch

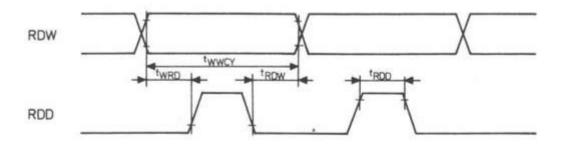

Bild 4: DMA-Operationen

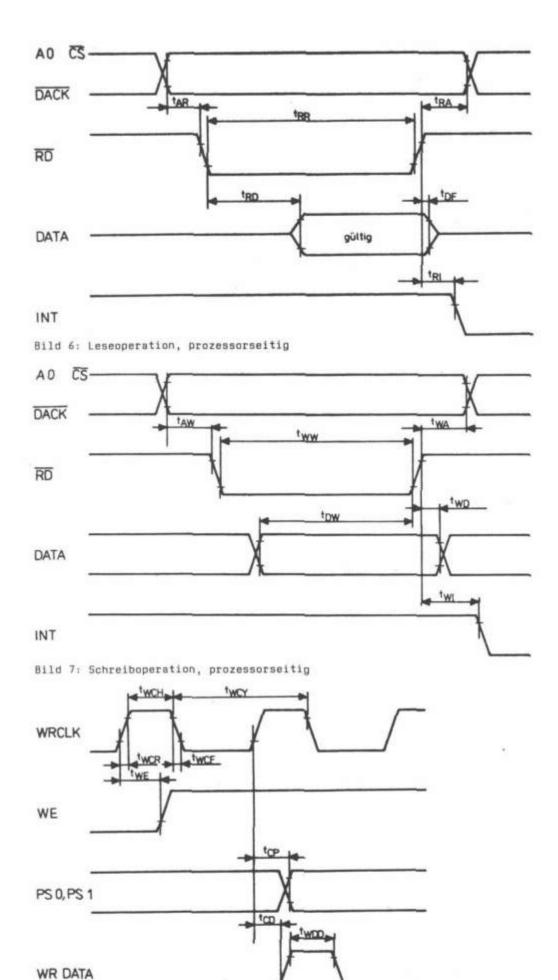

Bild 5: Leseoperation, laufwerkseitig

Bild 8: Schreiboperation, laufwerkseitig

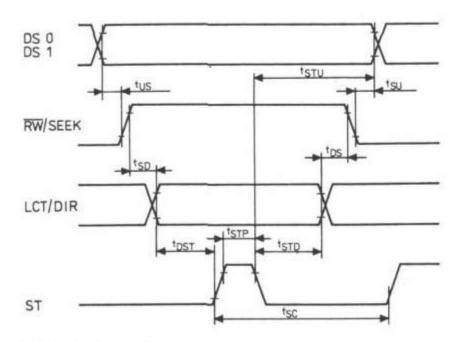

Bild 9: Suchoperationen

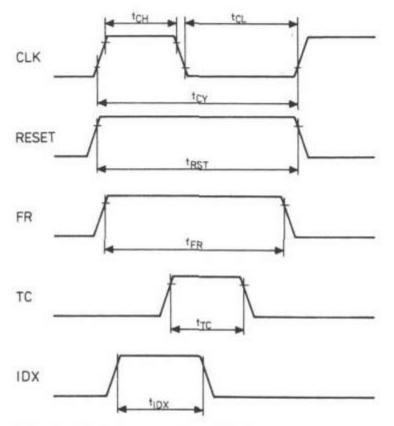

Bild 10: Impulsdach- und Flankenzeiten

#### Applikative Hinweise

Der U 8272 D kann in mit Floppy-Disk-Laufwerken ausgestatteten Mikrorechnern, Bürocomputern, Arbeitsplatzcomputern usw. zahlreiche Steuerungsaufgaben im Rahmen des Interfacespiels zwischen Prozessor bzw. CPU und den Floppy-Disk-Laufwerken ausführen.

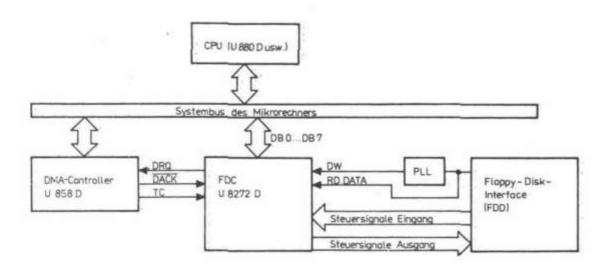

Besonders in Verbindung mit einem DMA-Controller (z. B. U 858 D) ermöglicht der U 8272 D relativ einfache Systemkonfigurationen für mit unterschiedlichsten CPU-Typen konzipierte Mikrorechner.

Bild 11: Systemkonfiguration mit DMA-Controller (Blockschaltbild)

Dieses Datenblatt gibt keine Auskunft über Liefermöglichkeiten und beinhaltet keine Verbindlichkeiten zur Produktion. Die gültige Vertragsunterlage beim Bezug der Bauelemente ist der Typstandard. Rechtsverbindlich ist jeweils die Auftragsbestätigung.

Änderungen im Sinne der technischen Weiterentwicklung vorbehalten!

Die Behandlungsvorschriften für MOS-Bauelemente müssen unbedingt eingehalten werden, da andernfalls eine Reklamation nicht anerkannt werden kann.

11/88

### veb mikroelektronik karl marx erfurt

DDR-5023 Erfurt, Rudolfstraße 47 Telefon 5.80, Telex 061 306

#### elektronik export import

Volkseigener Außenhandelsbetrieb der Deutschen Demokratischen Republik DDR - 1026 Berlin, Alexanderplatz 6 Telex. BLN 114721 elei, Telefon: 2180