# Information

## CMOS-Mikroprozessorsystem U84C00

Das Mikroprozessorsystem U 64 C 00 umfaßt ein Sortiment an Mikrorechnerbausteinen, welches so konzipiert ist, daß Mikrorechnersysteme mit minimaler Bausteinanzahl zu realisieren sind. Als Speicherbausteine sind sämtliche Standardbauolemente verwendbär. Alle Bausteine des Systems benötigen nur eine einzige 5 V-Stromversorgung und einen 5 V-Einphasentakt. Hervorzuheben ist der geringe Stromverbrauch der CMOS-Schaltkreise. Das Schaltkreissystem ist für den Einsatz in einem Temperaturbereich von 0 ... 70 °C geeignet.

#### Übersicht Mikroprozessorsystem U 84 C 00

| Funktion | 2,5 MHz         | A MHz           |

|----------|-----------------|-----------------|

| CPU      | U 84 C 00 DC 02 | U 84 C 00 DC 04 |

| 013      | U 84 C 20 DC 02 | U 84 C 20 DC 04 |

| CTC      | U 84 C 30 DC 02 | U 84 C 30 DC 84 |

| SIO      | U 84 D : DD 02  | U 84 C 40 DC 04 |

Die CPU ist ein in CMOS-Technologie hergestellter Einchipmikroprozessor. Sie ermöglicht den Aufbau von Mikroprozessorsystemen hoher Leistungsfähigkeit. Folgende Varianten werden vom MME gefertigt:

| Тур |    |   | Tak | tfrequenz | Stromaufnahme<br>(typisch) |     | Schlafzustand |       |   |               |

|-----|----|---|-----|-----------|----------------------------|-----|---------------|-------|---|---------------|

| IJ  | 84 | C | 00  | oc        | 02                         | 2,5 | MHz           | 15 m2 | 1 | miglich       |

| U   | 84 | C | 00  | DC        | 04                         | - 4 | MHZ           | 15 m/ |   | möglich       |

| IJ  | 84 | C | 0.0 | DC        | 02-1                       | 2,5 | MHZ           | 15 m/ | V | night moglich |

#### Eigenschaften der CPU:

- Der Befehlssatz enthält 158 Befehle mit 16-, 8-, 4- und Einzelbit-Instruktionen sowie zusätzliche Adressierweisen (indizierte, relative und Bitadressierung).

- Die minimale Befehlsausführzeit der Typen U B4 C 00 DC 02 und U B4 C 00 DC 02-1 beträgt 1,6 µs bei einer maximalen Taktfrequenz von 2,5 MHz.

Die minimale Befehlsausführzeit des U 84 C 00 DC 04 beträgt 1 µs bei einer maximalen Taktfrequenz von 4 MHz.

- Die CPU enthält 21 interne Register und einen Befehlszähler.

- Es existieren 3 schnelle Interruptbehandlungsarten und außerdem ein zusätzlicher, nicht maskierbarer Interrupt.

- 5 V-Einphasentakt und eine Standard-5 V-Gleichspannung

- Der Anschluß von dynamischen oder statischen Standardspeicherchips ist möglich.

- Integrierte dynamische Refresh-Hardware

- Die Eingänge sind voll ITL-kompatibel, die Ausgänge können eine Standard-TTL-Last treiben.

- Die CPU ist in einen Schlafzustand (Standby) überführhar, bei dem die Stromaufnahme kleiner als 10 μA ist (außer U 84 C 00 DC 02-1).

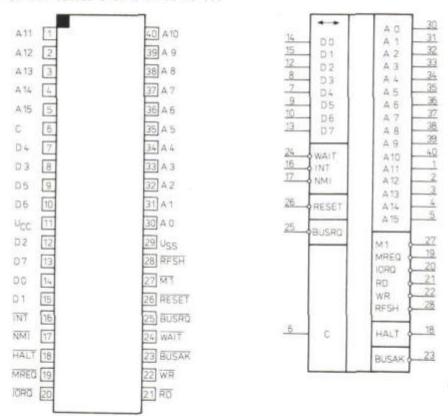

Bild 1: Anschlußbelegung und Schaltzeichen U 84 C 00 DC (Bauform 1)

#### Bezeichnung der Anschlüsse:

| A D A 15 | 16 bit-AureBbus, Ausgänge                       |

|----------|-------------------------------------------------|

| 0 0 0 7  | 8 bit bidirektionaler Datenbus                  |

| M 1      | Maschinenzyklus M 1, Ausgang                    |

| MREQ     | Speicheranforderung, Ausgang                    |

| IDRQ     | Ein-/Ausgabeanforderung, Ausgang                |

| RD       | Leseanforderung, Ausgang                        |

| WR       | Schreibanforderung, Ausgang                     |

| RESH     | Refreshsignal, Ausgang                          |

| HALT     | CPU im Software-Halt-Zustand, Ausgang           |

| WAIT     | Warteanforderung für die CPU, Eingang           |

| INT      | Interruptanforderung, Eingang                   |

| NMT      | nicht maskierbare Interruptanforderung, Eingang |

| RESET    | Rücksetzen, Eingang                             |

| BUSRQ    | Busanforderung, Eingang                         |

| BUSAK    | * Busanforderungsbestätigung, Ausgang           |

|          |                                                 |

#### Aufbau des CPU-Registersatzes:

#### Befehlsgruppen: - 8 bit Ladebefehle - Registertausch Hauptregistersatz Alternativsatz - 8 bit arithemtische und logische Befehle Akkumulator Flags Akkumulator Flags - Rotations- und Schiebebefehle - Ein- und Ausgabebefehle В C 8. - Rückkehrbefehle Register zur D. E+ - 16 bit arithemtische Befehle D E allgemeinen 11 H. - 16 bit Ladebefehle Verwendung + - Blocktransport- und Suchbefehle Speicher Refresh R - Steuerbefehle Interrupt Vektor I - Bitoperationen - Rufbefehle Indexregister IX - Sprungbefehle IY Spezial-Indexregister Kellerzeiger SP register DO. Programmzähler PC 8 bit - Datenbus Datenbussteuerung Arithmetisch-Betetils-Betehlslogische dekoder register interner Datenbus Einheit (ALU) und CPU-Steuerung CPU-Steuerung CPU-Register

Adressensteuerung

A 0 ... A 15

16 bit - Adrellbus

Bild 2: Blockschaltbild der CPU

IORQ MREQ

RESH

HALT

WAIT

BUSAK

RD

WR

INT

NMI RESET BUSRO Die PID ist ein in CMOS-Technologie hergestellter programmierbarer Ein-/Ausgabebaustein mit zwei TTL-kompatiblen Kanälen. Die PIO stellt die Verbindung zwischen der CPU und peripheren Geräten her, ohne daß zusätzliche Logik erforderlich ist.

Folgende Varianten werden vom MME gefertigt:

| Тур |    |   |    |    |      | Tak | tfrequenz |   | tromaufoahmo<br>typisch) | Schlafzustand |

|-----|----|---|----|----|------|-----|-----------|---|--------------------------|---------------|

| U   | 84 | C | 20 | DC | 02   | 2,5 | 2,5 MHz   | 2 | mA                       | moglich       |

| U   | 84 | C | 20 | UC | 0.4  | 4   | MHz       | 2 | mΑ                       | möglich       |

| U   | 84 | C | 20 | DC | 02-1 | 2,5 | MHz       | 2 | mA.                      | nicht möglich |

#### Eigenschaften der PID:

- Interruptmöglichkeit im Quittungsbetrieb für schnelle Anforderungsbearbeitung

- Folgende Betriebsarten sind möglich:

- \* Byte-Ausgabe (Betriebsart 0)

- · Byte-Eingabe (Betriebsart 1)

- \* Byte-Ein-/Ausgabe (bidirektionaler Betrieb, nur für Port A möglich)/(Betriebsart 2)

- \* Bit-Fin-/Ausgabe (Betriebsart 3)

- Die Interruptbearbeitung kann den Bedingungen des peripheren Gerätes angepaßt programmiert werden.

- Die Ein- und Ausgänge sind ITL-kompatibel.

- automatische Interruptvektorerzeugung und Prioritätskodlerung durch Kaskadierung der Bausteine

- Die Ausgänge des Ports B sind für den direkten Anschluß von Darlington-Transistoren geeignet.

- Die PIO ist in einen Schlafzustand überführbar, bei dem die Stromaufnahme kleiner als 10 µA wird (außer U 84 C 20 DC 02-1).

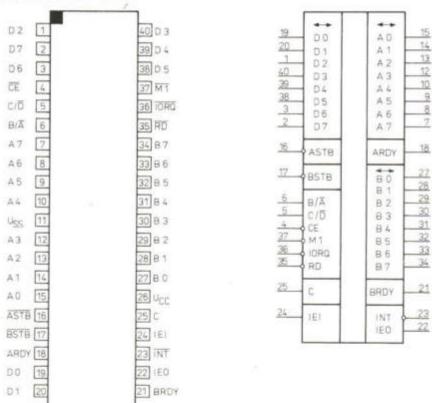

Sild J: Anschlußbelegung und Schaltzeichen U 84 C 20 DC (Bauform 1)

#### Bezeichnung der Anschlüsse:

| RO      | CPU-Leseanforderung, Eingang              |

|---------|-------------------------------------------|

| B/A     | Kanalauswahl, Eingang                     |

| C/D     | Umschaltung Steuerwort/Datenwort, Eingang |

| CE      | Bausteinauswahl, Eingang                  |

| M 1     | CPU-Maschinenzyklus M 1, Eingang          |

| TORQ    | CPU-Ein-/Ausgabeanforderung, Eingang      |

| BSTB    | Kanal-8-Strobe, Einjang                   |

| BRDY    | Kanal-B-Quittung, Ausgang                 |

| INT     | Interruptanforderung, Ausgang             |

| ASTB    | Kanal-A-Strobe, Eingang                   |

| ARDY    | Kanal-A-Quittung, Ausgang                 |

| IE1     | Interruptfreigabe, Eingang                |

| IEO     | Interruptfreigabe, Ausgang                |

| A 0 A 7 | Ein-/Ausgänge Port A                      |

| B 0 B 7 | Ein-/Ausgänge Port B                      |

| 0 0 0 7 | 8 bit bidirektionaler Datenbus            |

| C       | Systemtakt                                |

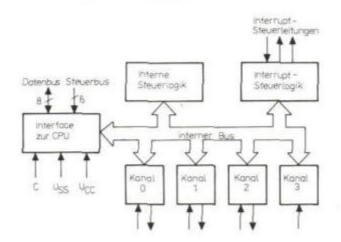

Bild 4: Blockschaltbild der P10

Der CTC ist ein in CMOS-Technologie hergestellter programmierbarer Zähler-/Zeitgeberbaustein, der über vier voneinander unabhängige, softwareprogrammierbare Zähler-/Zeitgeberkanäle verfügt.

Folgende Varianten werden vom MME gefertigt:

| Тур |    |              |    |    |      |     | tfrequenz | Stromaufnahme<br>(typisch) | Schlafzustand |

|-----|----|--------------|----|----|------|-----|-----------|----------------------------|---------------|

| IJ  | 84 | C            | 30 | DE | 02   | 2,5 | MHz       | 3. mA                      | möglich       |

| U.  | 84 | $\mathbb{C}$ | 30 | DC | 0.4  | 4   | MHZ       | 3 mA                       | möglich       |

| U   | 84 | C            | 30 | 30 | 02-1 | 2,5 | MHZ       | 3: mA                      | nicht möglich |

#### Eigenschaften des CTC:

- Alle Ein- und Ausgänge sind voll TTL-kompatibel.

- Es wird nur eine 5 V-Versorgungsspannung benötigt.

- Es existieren vier voneinander unabhängige, softwareprogrammierbare 8 bit-Zähler-/16 bit-Zeitgeberkanäle. Jeder dieser Kanäle kann wahlweise als Zähler oder Zeitgeber verwendet werden.

- In der Betriebsart Zeitgeber sind Vorteiler durch 16 oder 256 für jeden Zeitgeberkanal möglich.

- Es können Interrupts bei Erreichen von programmißig festgelegten Zähler- oder Zeitgeberwerten programmiert werden.

- automatische Interruptvektorbereitstellung und Prioritätskodierung ohne zusätzlichen Schaltungsaufwand durch Kaskadierung der Bausteine

- Die Ausgänge (ZC/TO 0 ... ZC/TO 2) der drei herausgeführten Kanäle sind zum direkten Anschluß von Darlington-Transistoren geeignet.

- Die maximale Zählfrequenz in der Betriebsart Zähler ist  $f_{\rho}/2$ .

- Der CTC ist in einen Schlafzustand überführbar, bei dem die Stromaufnahme kleiner als 10  $\mu A$  wird.

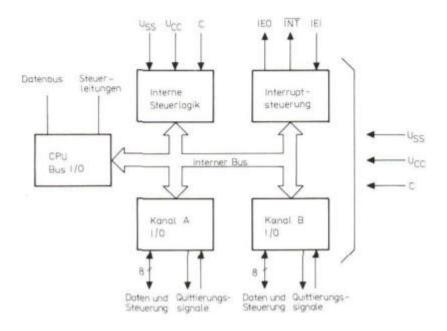

Der Zähler-/Zeitgeberbaustein enthält folgende Funktionseinheiten (siehe Blockschaltbild):

- Interface zur CPU

- Der CTC kann direkt über die interne Bus-Interface-Logik an die CPU angeschlossen werden.

- Interne Steuerlogik

- Über eine Interne Steuerlogik wird der Daten- und Steuerbus mit den vier Zähler-/Zeitgeberkanälen des CTC synchronisiert.

- Interrupt-Steuerlagik

- Die Interrupt-Steuerlogik behandelt die CPU-Interruptstrukturen entsprechend der festgelegten Priorität. Diese Priorität ist abhängig von der Stellung des CTC in der Prioritätskette. Jedem der vier Kanäle wird ein Interruptvektor zugeordnet, wobei der Kanal D die höchste Priorität besitzt.

- 4 Zähler-/Zeitgeberkanäle

- Jede Kanaleinheit besteht aus einem Zeitkonstantenregister (8 bit), einem Kanalsteuerregister (8 bit), einem Rückwärtszähler (8 bit), einem Vorteiler und einer eigenen Steuerlogik. Der Vorteiler (8 bit) ist auf die Werte 16 oder 256 programmiert.

Bild 5: Anschlußbelegung und Schaltzeichen U 84 C 30 DC (Bauform 2) Bezeichnung der Anschlüsse:

| IDED            | tin-/Ausgabeanforderung, Eingang                                       |

|-----------------|------------------------------------------------------------------------|

| IEI             | Interruptfreigabe, Eingang                                             |

| IEO             | Interruptfreigabe, Ausgang                                             |

| INT             | Interruptanforderung, Ausgang                                          |

| RII             | CPU-Leseanforderung, Eingang                                           |

| 1 M             | CPU-Maschinenzyklus, Eingang                                           |

| C.              | Systemtakt, Eingang                                                    |

| RESET           | Rücksetzeingang                                                        |

| C/TRG D C/TRG 3 | Takt- bzw. Triggereingang für den jeweiligen Kanal                     |

| D D D 7         | 8 bit Datenbus, Ein-/Ausgänge, tristate                                |

| ZC/TO 0 ZC/TO 2 | Nulldurchgang des Rückwärtszählers bzw. Zeitgebermeldung               |

| KS 0, KS 1      | Kanalauswahl, Eingabe einer 2 bit Adresse des vom Mikroprozesser ange- |

|                 | sprochenen Kanals                                                      |

Bild 6: Blockschaltbild des CTC

Die SIO ist ein in CMOS-Technologie hergestellter, programmierbarer, zweikanaliger Baustein, der Daten in das für serielle Datenübertragung erforderliche Format umsetzt. Sie kann asynchron, synchron und bitorientiert synchron arbeiten.

Folgende Varianten werden vom MME gefertigt: -

| Тур |    |   |    |    |    | Taktfrequenz | Stromaufnahme<br>(typisch) | Schlafzustand |

|-----|----|---|----|----|----|--------------|----------------------------|---------------|

| U   | 84 | C | 40 | DC | 02 | 2,5 MHz      | 7 mA                       | müglich       |

| U   | 84 | C | 40 | DC | 04 | 4 8912       | . 7 mA                     | möglich       |

#### Eigenschaften der 510:

- vier unabhängige serielle Ports

- zwei Sender- sowie Empfängerports

- asynchrone oder synchrone Arbeitsweise

- asynchrone Daten mit 5, 6, 7 oder 8 Datenbits, 1, 1 1/2 oder 2 Stoppbits und gerader, ungerader oder keiner Paritätserzeugung bzw. Peritätsprüfung

- Paritats-, überlauf- und Rahmenfehlererkennung

- Breakerzeugung und -erkennung

- alle Ein- und Ausgänge voll ITL-kompatibel

- Taktvarianten: x 1, x 16, x 32, x 64

- Datenübertragungsraten: O bis 550 kbit/sec.

- 4 Eingänge/4 Ausgänge zur MODEM-Steuerung

- volle Fähigkeit zur Arbeit nach HOLC einschließlich Verarbeitung des I-Feld-Restes

- interne oder externe Zeichensynchronisation mit automatischer Einfügung von Synchronisationszeichen und Flags

- Betriebszustand "AdreBerkennung" bei SDLC/HDLC

- Betriebszustand "Synchronisationsbyteunterdrückung" mit wonn- und bisynchroner Arbeitsweise

- Die hohen übertragungsraten und die automatische CRC-Erzeugung gestatten die direkte Zusammenschaltung mit Floppy-Disk-Speichern doppelter Dichte, ohne daß direkter Speicherzugriff erforderlich ist.

- Empfangene Daten und Fehlerregister sind vierfach, zu sendende zweifach gepuffert.

- leistungsfähige Interruptstruktur durch wahlweise festen oder variablen Interruptvektor

- CRC-16- oder CRC-CCITT-(0 und -1)-Prüfpolynom

- gültig empfangene Daten vor dem Überschreiben geschützt

- 5 V-Einphasentakt und eine einzige 5 V-Gleichspannungsversorgung

- Prioritätslogik durch Kaskadierung der Bausteine

- Die 510 kann in einen Schlafzustand überführt werden, in dem die Stromaufnahme kleiner als 10 μA wird.

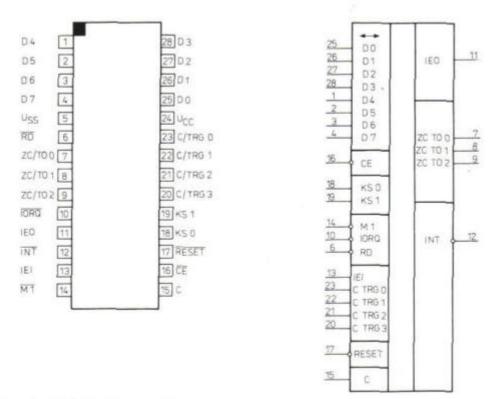

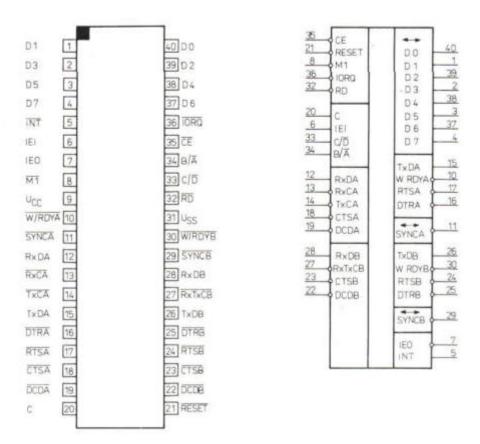

Bild 7: Anschlußbelegung und Schaltzeichen (Bondvariante U B4 E 40 DE/Bauform 1)

Bild B: Anschlußbelegung und Schaltzeichen (Bondvariante U 84 C 41 DC/Bauform 1)

#### Bezeichnung der Anschlüsse:

```

8 bit bidirektionaler Datenbus

00 ... 07

Bausteinauswahl, Eingang

CE

RESET

Rücksetzen, Eingang

MI

CPU-Maschinenzyklus M 1, Eingang

CPU-Ein-/Ausgabeanforderung, Eingang

IDRO

CPU-Leseanforderung, Eingang

RD

Empfangsdaten, Eingänge

RxDA, RxDB

Empfängertakte, Eingänge<sup>1)</sup>

RXCA, RXCB

TXCA, TXCB

Sendertakto, Eingänge<sup>1</sup>

CISA, CISB

Sendebereitschaft, Eingänge

DEDA, DEDR

Datenträgererkennung, Eingänge

Kanalauswahl, Eingang

B/A

Umschaltung Steuerwort/Datenwort, Eingang

C/D

Interruptfreigabe, Eingang

ILI

1E0

Interruptfreigabe, Ausgang

INT

Interruptanforderung, Ausgang

Sendedaten, Ausgänge

TxDA, TxDB

W/ROYA, W/ROYB

WAIT/READY-Pin (CPU WAIT, DMA READY), Ausglinge

SYNCA, SYNCB

Externsynchronisation, Ein-/Ausgänge

RISA, RISB

Sendesnforderung, Ausgänge

Systemtakt

DIRA, DIRB

Bereitschaft Datenterminal, Ausgänge

```

1) Empfänger- und Sendetakt Kanal B gemeinsam gebondet (U R4 C 40), Pinbezeichnung: RxTxCB

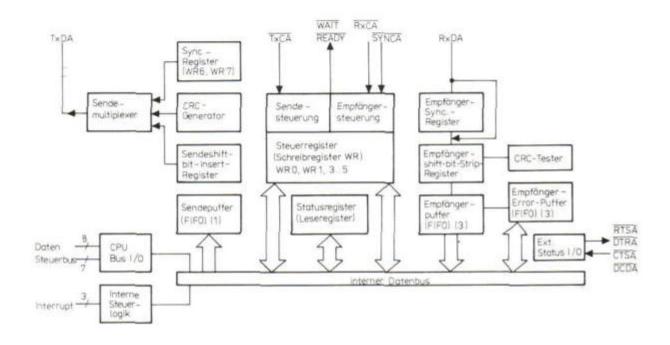

Bild 9: Struktur des SIO-Kanals A

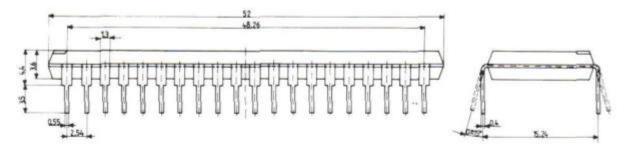

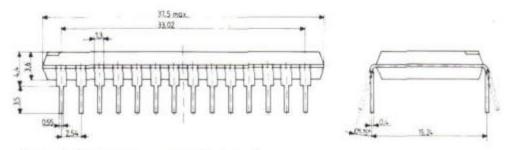

Bild 10: Gehäuseabwessungen Bauform 1

Bild 11: Gehäuseabmessungen Bauform 2

Dieses Datenblatt gibt keine Auskunft über Liefermöglichkeiten und beinhaltet keine Verbind-Tichkeiten zur Produktion. Die gültigen Vertragsunterlagen beim Bezug der Bauelemente sind die Typenstandards. Rechtsverbindlich ist jeweils die Auftragsbestätigung.

Anderungen im Zuge der technischen Weiterentwicklung vorbehalten.

Die Hehandlungsvorschriften für MOS-Bauelemente müssen unbedingt eingehalten werden, da andernfalls eine Reklamation nicht anerkannt werden kann.

11/88

veb mikroelektronik karl marx erfurt stammbetrieb

DDR-5023 Erfurt, Rudalfstraße 47 Telefon 5-80, Telex 061-306

### elektronik export-import

Volkseigener Außenhandelsbetrieb der Deutschen Demokratischen Republik DDR - 1026 Berlin, Alexanderplatz 6 Telex: BLN 114721 elei, Telefon: 2180